21F02-F.I.N • 21F02-2 - F.I.N • 21F02-4 - F.I.N

# **DESCRIPTION**

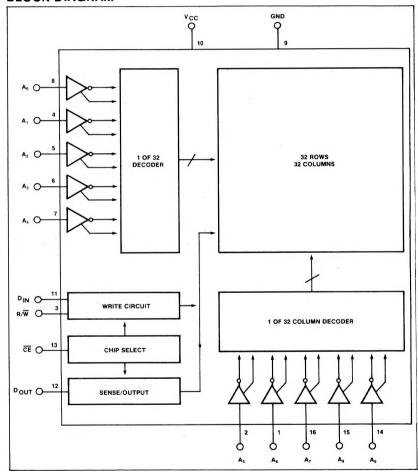

The 21F02 is a high speed static random access memory element using n-channel MOS devices integrated on a monolithic array. It uses fully do stable (static) circuitry and therefore requires no clocks or refreshing to operate. The data is read out nondestructively and has the same polarity as the input data.

The 21F02 is designed for memory applications where high performance, low cost, large bit storage, and simple interfacing are important design objectives. A separate chip enable (CE) lead allows easy selection of an individual package when outputs are OR-tied.

The Signetics 21F02 is fabricated with nchannel silicon gate technology. This technology allows the design and production of high performance easy to use MOS circuits and provides a higher functional density on a monolithic chip than either conventional MOS technology or p-channel silicon gate technology.

## **FEATURES**

- Fully TTL compatible

- Single 5V supply

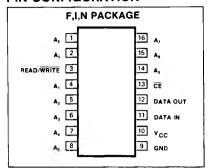

# **PIN CONFIGURATION**

## **BLOCK DIAGRAM**

21F02-F,I,N • 21F02-2 - F,I,N • 21F02-4 - F,I,N

# **ABSOLUTE MAXIMUM RATINGS**1

|       | PARAMETER                                                    | RATING     | UNIT |  |  |

|-------|--------------------------------------------------------------|------------|------|--|--|

|       | Temperature range                                            |            | °C   |  |  |

| TSTG  | Storage                                                      | -65 to 150 |      |  |  |

| $P_D$ | Power dissipation <sup>2</sup>                               |            |      |  |  |

|       | N package                                                    | 640        | mW   |  |  |

|       | F package                                                    | 1          | w    |  |  |

|       | I package                                                    | 1          | w    |  |  |

|       | All input, output and supply voltages with respect to ground | -0.5 to 7  | V    |  |  |

# DC ELECTRICAL CHARACTERISTICS T<sub>A</sub> = 0°C to 70°C, V<sub>CC</sub> = 5V ± 5% unless otherwise specified.

|                        |                                     | • • • • • • • • • • • • • • • • • • • •                                           |             |                  |            |      |  |  |

|------------------------|-------------------------------------|-----------------------------------------------------------------------------------|-------------|------------------|------------|------|--|--|

|                        | DADAMETED                           | TEST CONDITIONS                                                                   |             |                  |            |      |  |  |

|                        | PARAMETER                           | TEST CONDITIONS                                                                   | Min         | Typ <sup>3</sup> | 0.8<br>Vcc | UNIT |  |  |

| VIL<br>VIH             | Input voltage<br>Low<br>High        |                                                                                   | -0.5<br>2.0 |                  |            | V    |  |  |

| V <sub>OL</sub><br>Voh | Output voltage<br>Low<br>High       | I <sub>OL</sub> = 2.1mA<br>I <sub>OH</sub> = -100μA                               | 2.4         |                  | 0.4        | V    |  |  |

| ILI                    | Input load current (All input pins) | V <sub>IN</sub> = 0 to 5.25V                                                      |             |                  | 10         | μА   |  |  |

| ILOH<br>ILOL           | Output leakage current              | CE = 2.0V<br>V <sub>OUT</sub> = 2.4 to V <sub>CC</sub><br>V <sub>OUT</sub> = 0.4V |             |                  | 5<br>-10   | μА   |  |  |

| ICC1                   | Supply current                      | All inputs = 5.25V, Data out open $T_A = 25^{\circ}C$ $T_A = 0^{\circ}C$          |             | 30               | 60<br>70   | mA   |  |  |

AC ELECTRICAL CHARACTERISTICS  $T_A = 0$ °C to 70°C,  $V_{CC} = 5V \pm 5\%$  unless otherwise specified, Input pulse levels = 0.65 to 2.2V, Input pulse rise and fall times = 20ns, Timing measurement reference level = 1.5V, Output load = 1 TTL gate and C<sub>L</sub> = 100pF

|                          |                                                                            |                                    |                                        | 21F02                 |                  | 21F02-2    |                       | 21F02-4          |            |                       |      |            |                |

|--------------------------|----------------------------------------------------------------------------|------------------------------------|----------------------------------------|-----------------------|------------------|------------|-----------------------|------------------|------------|-----------------------|------|------------|----------------|

| 1                        | PARAMETER                                                                  | то                                 | FROM                                   | Min                   | Typ <sup>3</sup> | Max        | Min                   | Typ <sup>3</sup> | Max        | Min                   | Typ3 | Max        | UNIT           |

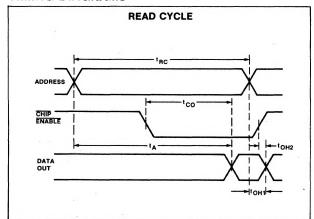

| trc<br>ta<br>tco         | READ CYCLE<br>Read cycle<br>Access time                                    | Output time                        | Chip enable                            | 350                   |                  | 350<br>180 | 250                   |                  | 250<br>130 | 450                   |      | 450<br>230 | ns<br>ns<br>ns |

| ton1                     | Previous read data valid<br>with respect to<br>Address<br>Chip enable      |                                    |                                        | 40<br>0               |                  |            | 40<br>0               |                  |            | 40<br>0               |      |            | ns             |

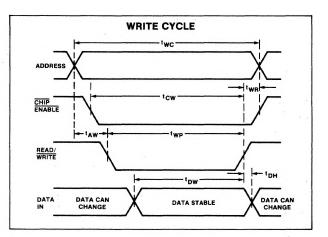

| twc<br>twp<br>twn        | WRITE CYCLE Write cycle Write pulse width Write recovery time              |                                    |                                        | 350<br>250<br>20      |                  |            | 250<br>180<br>20      |                  |            | 450<br>300<br>20      |      |            | ns<br>ns<br>ns |

| taw<br>tow<br>toh<br>tcw | Setup and hold time<br>Setup time<br>Setup time<br>Hold time<br>Setup time | Write<br>Output<br>Output<br>Write | Address<br>Data<br>Data<br>Chip enable | 20<br>250<br>0<br>250 |                  |            | 20<br>180<br>0<br>180 |                  |            | 20<br>300<br>0<br>300 |      |            | ns             |

NOTES on following page.

21F02-F,I,N • 21F02-2 - F,I,N • 21F02-4 - F,I,N

## NOTES

- Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device of these or any other condition above those indicated in the operation sections of this specification is not implied.

- For operating at elevated temperatures the device must be derated based on a +150°C

maximum junction temperature and a thermal resistance of 150°C/W junction to

ambient (B package).

- 3. Typical values are at +25°C and typical supply voltages.

- 4. All inputs protected against static charge.

- 5. Parameter valid over operating temperature range unless otherwise specified.

- 6. All voltage measurements are referenced to ground.

- Manufacturer reserves the right to make design and process changes and improvements.

## **TIMING DIAGRAMS**