# 64-BIT BIPOLAR SCRATCH PAD | 3101A

**FEBRUARY 1975**

# DIGITAL 8000 SERIES TTL/MEMORY

#### **DESCRIPTION**

The 3101A is a 64-bit, Schottky clamped TTL, Read-Write Random Access Memory ideal for use in scratch pad and high-speed buffer memory applications.

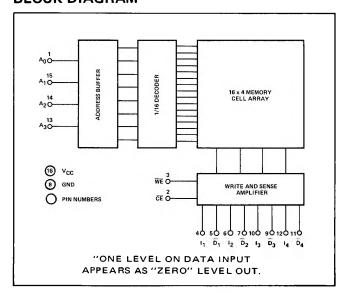

The 3101A is a fully decoded memory array organized as 16 words of 4 bits each, with separate input and output lines. It features PNP inputs, one chip enable line, and open collector outputs for ease of memory expansion.

The outputs of the 3101A assume a logic "1" state during write. This allows both memory inputs and outputs to share a common bus for minimizing interconnections, and more effective utilization of common I/O circuitry.

The 3101A is available in the commercial and military temperature ranges. For the commercial temperature range (0°C to +75°C) specify N3101A, B or F. For the military temperature range (-55°C to +125°C) specify S3101A, F only.

#### **FEATURES**

- ORGANIZATION 16 X 4

- ADDRESS ACCESS TIME:

S3101A 50ns, MAXIMUM

N3101A 35ns, MAXIMUM

- WRITE CYCLE TIME:

S3101A 25ns, MAXIMUM

N3101A 25ns, MAXIMUM

- POWER DISSIPATION 6.25mW/BIT, TYPICAL

- INPUT LOADING:

S3101A (-150μA) MAXIMUM

N3101A (-100μA) MAXIMUM

- OUTPUT BLANKING DURING WRITE

- ON-CHIP ADDRESS DECODING

- OPEN COLLECTOR OUTPUTS

- 16 PIN CERAMIC DIP

**APPLICATIONS**

SCRATCH PAD MEMORY BUFFER MEMORY PUSH DOWN STACKS

CONTROL STORE

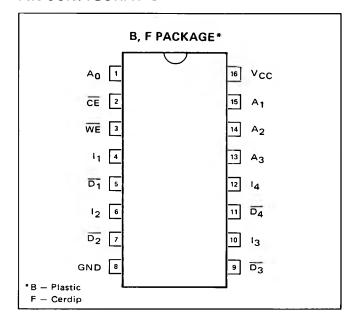

#### PIN CONFIGURATION

#### **TRUTH TABLE**

| MODE      | CE | WE | IN | $\overline{D}_N$             |

|-----------|----|----|----|------------------------------|

| READ      | 0  | 1  | ×  | Complement<br>of Data Stored |

| WRITE "0" | 0  | 0  | 0  | 1                            |

| WRITE "1" | 0  | 0  | _1 | 1                            |

| DISABLED  | 1  | Х  | Х  | 1                            |

X = Don't care.

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

|                  | PARAMETER <sup>1</sup>                              | RATING                      | UNIT     |

|------------------|-----------------------------------------------------|-----------------------------|----------|

| V <sub>CC</sub>  | Power Supply Voltage                                | +7                          | Vdc      |

| V <sub>in</sub>  | Input Voltage                                       | +5.5                        | Vdc      |

| VOH              | High Level Output Voltage                           | +5.5                        | Vdc      |

| TA               | Operating Temperature Range<br>(N3101A)<br>(S3101A) | 0° to +75°<br>-55° to +125° | °c<br>°c |

| T <sub>stg</sub> | Storage Temperature Range                           | -65° to +150°               | °C       |

# $\begin{array}{ll} \textbf{ELECTRICAL CHARACTERISTICS} & \text{S3101A} & -55^{\circ}\text{C} \leqslant \text{T}_{A} \leqslant +125^{\circ}\text{C}, \, 4.5\text{V} \leqslant \text{V}_{CC} \leqslant 5.5\text{V} \\ \text{N3101A} & 0^{\circ}\text{C} \leqslant \text{T}_{A} \leqslant +75^{\circ}\text{C}, \, 4.75\text{V} \leqslant \text{V}_{CC} \leqslant 5.25\text{V} \\ \end{array}$

| PARAMETER        |                         | TEST CONDITIONS                                                      | S3101A <sup>1,2,3</sup> |                  |       | N3101A <sup>1,2,3</sup> |                  |      |      |

|------------------|-------------------------|----------------------------------------------------------------------|-------------------------|------------------|-------|-------------------------|------------------|------|------|

|                  |                         |                                                                      | MIN                     | TYP <sup>8</sup> | MAX   | MIN                     | TYP <sup>8</sup> | MAX  | UNIT |

| IIL              | "0" Input Current       | V <sub>IN</sub> = 0.45V                                              |                         | -10              | - 150 |                         | -10              | -100 | μΑ   |

| Чн               | "1" Input Current       | V <sub>IN</sub> = 5.5V                                               |                         |                  | 25    |                         |                  | 10   | μΑ   |

| VIL              | "0" Level Input Voltage | V <sub>CC</sub> = MIN                                                |                         |                  | .80   |                         |                  | .85  | v    |

| VIH              | "1" Level Input Voltage | V <sub>CC</sub> = MAX                                                | 2.0                     |                  |       | 2.0                     |                  |      | v    |

| V <sub>IC</sub>  | Input Clamp Voltage     | I <sub>IN</sub> = -12mA, V <sub>CC</sub> = MIN<br>(Note 6)           |                         |                  |       |                         | -1.0             | -1.5 | V    |

|                  |                         | I <sub>IN</sub> = -18mA, V <sub>CC</sub> = MIN<br>(Note 6)           |                         | -0.8             | -1.2  |                         |                  |      | \ \  |

| VOL              | "0" Output Voltage      | I <sub>OUT</sub> = 16mA, V <sub>CC</sub> = MIN<br>(Notes 4, 5)       |                         | 0.35             | 0.5   |                         | 0.35             | 0.45 | V    |

| C <sub>IN</sub>  | Input Capacitance       | V <sub>IH</sub> = 2.0V, V <sub>CC</sub> = 5.0V                       |                         | 5                |       |                         | 5                |      | pF   |

| C <sub>OUT</sub> | Output Capacitance      | $\frac{V_{OUT}}{CE} = 2.0V, V_{CC} = 5.0V,$                          |                         | 8                |       |                         | 8                |      | pF   |

| Icc              | Power Supply Current    | (Note 5)                                                             |                         | 80               | 105   |                         | 80               | 105  | mA   |

| I <sub>OLK</sub> | Output Leakage Current  | CE = "1", V <sub>OUT</sub> = 5.5V,                                   |                         | <1               | 100   |                         | <1.0             | 100  | μΑ   |

|                  |                         | $V_{CC} = MIN$ $\overline{CE} = "1", V_{OUT} = 2.4V,$ $V_{CC} = MIN$ |                         | <1               | 40    |                         |                  |      | μΑ   |

#### NOTES:

- 1. All voltage measurements are referenced to the ground terminal. Terminals not specifically referenced are left electrically open.

- 2. Positive current is defined as into the terminal referenced.

- 3. Positive logic definition: "1" = HIGH  $\approx$  +5.0V; "0" = LOW  $\approx$  GRD.

- 4. Output sink current is supplied through a resistor to V<sub>CC</sub>.

- 5. All sense outputs in "0" state.

- 6. Test each input one at a time.

- 7. To guarantee a WRITE into the slowest bit.

- 8. Typical values are at  $V_{CC}$  = +5.0V and  $T_A$  = +25°C.

# SWITCHING CHARACTERISTICS $\begin{array}{ll} \text{S3101A} & -55^{\circ}\text{C} \leqslant \text{T}_{\text{A}} \leqslant +125^{\circ}\text{C}, \, 4.5\text{V} \leqslant \text{V}_{\text{CC}} \leqslant 5.5\text{V} \\ \text{N3101A} & 0^{\circ}\text{C} \leqslant \text{T}_{\text{A}} \leqslant +75^{\circ}\text{C}, \, 4.75\text{V} \leqslant \text{V}_{\text{CC}} \leqslant 5.25\text{V} \\ \end{array}$

| DADAMETED        |                                     | TEST CONDITIONS       | S3101A |                  |     | N3101A |                  |     |      |

|------------------|-------------------------------------|-----------------------|--------|------------------|-----|--------|------------------|-----|------|

|                  | PARAMETER                           | TEST CONDITIONS       | MIN    | TYP <sup>8</sup> | MAX | MIN    | TYP <sup>8</sup> | MAX | UNIT |

| Propaga          | tion Delays                         |                       |        |                  |     |        |                  |     |      |

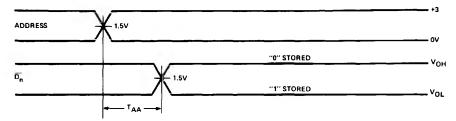

| TAA              | Address Access Time                 |                       |        | 25               | 50  | 10     |                  | 35  | ns   |

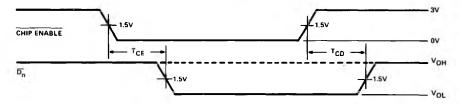

| TCE              | Chip Enable Access Time             |                       |        | 12               | 25  | 5      |                  | 17  | ns   |

| T <sub>CD</sub>  | Chip Enable Output Disable Time     |                       |        | 12               | 25  | 5      |                  | 17  | ns   |

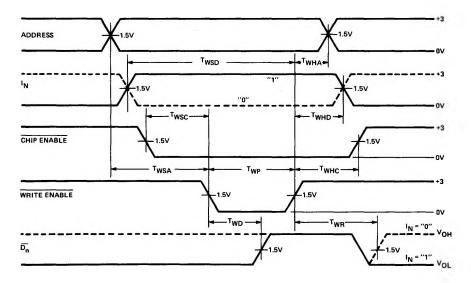

| T <sub>WD</sub>  | Write Enable to Output Disable Time |                       |        | 15               | 25  |        |                  | 20  | ns   |

| T <sub>WR</sub>  | Write Recovery Time                 | $R_1 = 270\Omega$     |        | 22               | 40  |        |                  | 35  | ns   |

| Write Se         | et-up Times                         | $R_2 = 600\Omega$     |        |                  |     |        |                  |     |      |

| TWSA             | Address to Write Enable             | C <sub>L</sub> = 30pF | 0      |                  |     | 0      | -8               |     | ns   |

| Twsp             | Data In to Write Enable             |                       | 25     |                  |     | 20     | 5                |     | ns   |

| Twsc             | CE to Write Enable                  |                       | 0      |                  |     | 0      | -5               |     | ns   |

| Write H          | old Times                           |                       |        |                  |     |        |                  |     |      |

| TWHA             | Address to Write Enable             |                       | 0      |                  |     | 0      |                  |     | ns   |

| T <sub>WHD</sub> | Data In to Write Enable             |                       | 0      |                  |     | 0      | -3               |     | ns   |

| T <sub>WHC</sub> | CE to Write Enable                  |                       | 0      |                  |     | 0      |                  |     | ns   |

| T <sub>WP</sub>  | Write Enable Pulse Width (Note 7)   |                       | 25     | 18               |     | 25     | 18               |     | ns   |

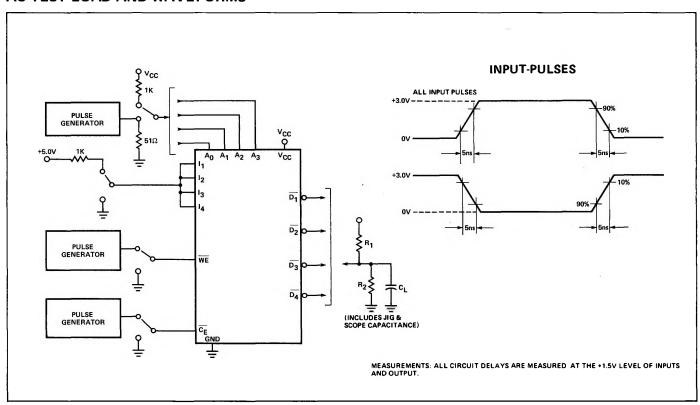

### **AC TEST LOAD AND WAVEFORMS**

# SWITCHING PARAMETERS MEASUREMENT INFORMATION

## ADDRESS ACCESS TIME

#### **CHIP ENABLE/DISABLE TIMES**

### **WRITE CYCLE**

#### **MEMORY TIMING DEFINITIONS**

| T <sub>WR</sub> | Delay between end of WRITE ENABLE pulse and when DATA OUTPUT becomes valid. (Assuming ADDRESS still valid—not as shown.) |                  | Required delay between end of WRITE ENABLE pulse and end of valid INPUT DATA.           |

|-----------------|--------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------|

|                 |                                                                                                                          |                  | Width of WRITE ENABLE pulse.                                                            |

| T <sub>CE</sub> | (with ADDRESS valid) and when DATA OUTPUT                                                                                |                  | Required delay between beginning of valid ADD-RESS and beginning of WRITE ENABLE pulse. |

| T <sub>CD</sub> | and DATA OUTPUT is in off state.                                                                                         |                  | Required delay between beginning of valid DATA INPUT and end of WRITE ENABLE pulse.     |

| TAA             |                                                                                                                          |                  | Delay between beginning of WRITE ENABLE pulse and when DATA OUTPUT is in off state.     |

| ,               |                                                                                                                          |                  | Required delay between end of WRITE ENABLE pulse and end of CHIP ENABLE.                |

| Twsc            | Required delay between beginning of valid CHIP ENABLE and beginning of WRITE ENABLE pulse.                               | T <sub>WHA</sub> | Required delay between end of WRITE ENABLE pulse and end of valid ADDRESS.              |