# 54/74174 54S/74S174 54LS/74LS174

**HEX D FLIP-FLOP**

**DESCRIPTION** — The '174 is a high speed hex D flip-flop. The device is used primarily as a 6-bit edge-triggered storage register. The information on the D inputs is transferred to storage during the LOW-to-HIGH clock transition. The device has a Master Reset to simultaneously clear all flip-flops.

- EDGE-TRIGGERED D-TYPE INPUTS

- BUFFERED POSITIVE EDGE-TRIGGERED CLOCK

- ASYNCHRONOUS COMMON RESET

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                                | PKG  |  |  |  |

|--------------------|-----|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|--|--|--|

| PKGS               | оит | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{ C to} + 125^{\circ}\text{ C}$ | TYPE |  |  |  |

| Plastic<br>DIP (P) | Α   | 74174PC,<br>74S174PC, 74LS174PC                                                          |                                                                                               | 9B   |  |  |  |

| Ceramic<br>DIP (D) | Α   | 74174DC,<br>74S174DC, 74LS174DC                                                          | 54174DM,<br>54S174DM, 54LS174DM                                                               | 6B   |  |  |  |

| Flatpak<br>(F)     | Α   | 74174FC,<br>74S174FC, 74LS174FC                                                          | 54174FM,<br>54S174FM, 54LS174FM                                                               | 4L   |  |  |  |

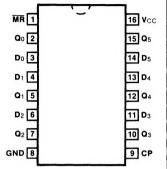

# CONNECTION DIAGRAM PINOUT A

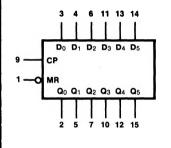

### LOGIC SYMBOL

V<sub>CC</sub> = Pin 16 GND = Pin 8

### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                                                                      | DESCRIPTION                                                                                          | <b>54/74 (U.L.)</b><br>HIGH/LOW        | <b>54/74S (U.L.)</b><br>HIGH/LOW               | <b>54/74LS (U.L.)</b><br>HIGH/LOW                   |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------|-----------------------------------------------------|

| D <sub>0</sub> — D <sub>5</sub><br>CP<br>MR<br>Q <sub>0</sub> — Q <sub>5</sub> | Data Inputs Clock Pulse Input (Active Rising Edge) Master Reset Input (Active LOW) Flip-Flop Outputs | 1.0/1.0<br>1.0/1.0<br>1.0/1.0<br>20/10 | 1.25/1.25<br>1.25/1.25<br>1.25/1.25<br>25/12.5 | 0.5/0.25<br>0.5/0.25<br>0.5/0.25<br>10/5.0<br>(2.5) |

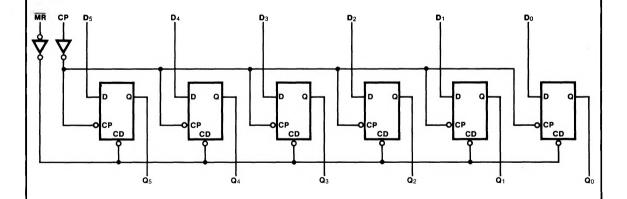

FUNCTIONAL DESCRIPTION — The '174 consists of six edge-triggered D flip-flops with individual D inputs and Q outputs. The Clock (CP) and Master Reset (MR) are common to all flip-flops. Each D input's state is transferred to the corresponding flip-flop's output following the LOW-to-HIGH Clock (CP) transition. A LOW input to the Master Reset (MR) will force all outputs LOW independent of Clock or Data inputs. The '174 is useful for applications where the true output only is required and the Clock and Master Reset are common to all storage elements.

**TRUTH TABLE**

| INPUTS                    | OUTPUTS  |

|---------------------------|----------|

| @ t <sub>n</sub> , MR = H | @ tn + 1 |

| Dn                        | Qn       |

| Н                         | Н        |

| L                         | L        |

tn = Bit time before positive-going clock transition

tn + 1 = Bit time after positive-going clock transition

H = HIGH Voltage Level L = LOW Voltage Level

#### LOGIC DIAGRAM

## DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER            | 54/74 |     | 54/748 |     | 54/74LS |     | UNITS | CONDITIONS                                                                                               |

|--------|----------------------|-------|-----|--------|-----|---------|-----|-------|----------------------------------------------------------------------------------------------------------|

|        |                      | Min   | Max | Min    | Max | Min     | Max |       |                                                                                                          |

| lcc    | Power Supply Current |       | 65  |        | 144 |         | 26  | mA    | $V_{CC} = Max$ $D_n = \overline{MR} = 4.5 \text{ V}$ $CP = \phantom{AAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAA$ |

# AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ} \text{ C}$ (See Section 3 for waveforms and load configurations)

|                                      |                                           | 54/74    | 54/74S                              | 54/74LS  |       |                 |  |

|--------------------------------------|-------------------------------------------|----------|-------------------------------------|----------|-------|-----------------|--|

| SYMBOL                               |                                           |          | $C_L = 15 pF$<br>$R_L = 280 \Omega$ |          | UNITS | CONDITIONS      |  |

|                                      |                                           | Min Max  | Min Max                             | Min Max  |       | !               |  |

| f <sub>max</sub>                     | Maximum Clock Frequency                   | 25       | 75                                  | 30       | MHz   | Figs. 3-1, 3-8  |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CP to Q <sub>n</sub> | 30<br>35 | 12<br>17                            | 25<br>22 | ns    | Figs. 3-1, 3-8  |  |

| tPHL                                 | Propagation Delay MR to Qn                | 35       | 22                                  | 35       | ns    | Figs. 3-1, 3-16 |  |

# AC OPERATING REQUIREMENTS: V<sub>CC</sub> = +5.0 V, T<sub>A</sub> = +25° C

| SYMBOL                                   | PARAMETER                                      | 54.        | 54/74 |            | 54/748 |            | 4LS | UNITS | CONDITIONS  |

|------------------------------------------|------------------------------------------------|------------|-------|------------|--------|------------|-----|-------|-------------|

|                                          | · ANAM= I=II                                   | Min        | Max   | Min        | Max    | Min        | Max | 00    | 00110110110 |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>D <sub>n</sub> to CP | 20<br>20   |       | 5.0<br>5.0 |        | 10<br>10   |     | ns    | Fig. 3-6    |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time HIGH or LOW<br>D <sub>n</sub> to CP  | 5.0<br>5.0 |       | 3.0<br>3.0 |        | 5.0<br>5.0 |     | ns    | 1 1g. 0 0   |

| tw (H)                                   | CP Pulse Width HIGH                            | 20         |       | 7.0        |        | 18         |     | ns    | Fig. 3-8    |

| t <sub>w</sub> (L)                       | MR Pulse Width LOW                             | 20         |       | 7.0        |        | 18         |     | ns    | Fig. 3-16   |

| t <sub>rec</sub>                         | Recovery Time MR to CP                         | 25         |       | 5.0        |        | 12         |     | ns    | 1           |