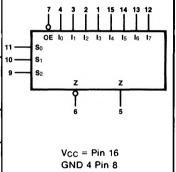

16 V<sub>CC</sub>

15 l<sub>4</sub>

14 l<sub>5</sub>

13 l<sub>6</sub>

12 l<sub>7</sub>

11 S<sub>0</sub>

10 S<sub>1</sub>

9 S<sub>2</sub>

CONNECTION DIAGRAM

PINOUT A

# 54S/74S251 54LS/74LS251

8-INPUT MULTIPLEXER

(With 3-State Outputs)

Z 6

OE 7

GND 8

**DESCRIPTION** — The '251 is a high speed 8-input digital multiplexer. It provides, in one package, the ability to select one bit of data from up to eight sources. It can be used as universal function generator to generate any logic function of four variables. Both assertion and negation outputs are provided.

- MULTIFUNCTIONAL CAPABILITY

- ON-CHIP SELECT LOGIC DECODING

- INVERTING AND NON-INVERTING 3-STATE OUTPUTS

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                              | PKG<br>TYPE |  |

|--------------------|-----|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------|--|

| PKGS               | OUT | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{C to} + 125^{\circ}\text{C}$ |             |  |

| Plastic<br>DIP (P) | A   | 74S251PC, 74LS251PC                                                                      |                                                                                             | 9B          |  |

| Ceramic<br>DIP (D) | Α   | 74S251DC, 74LS251DC                                                                      | 54S251DM, 54LS251DM                                                                         | 6B          |  |

| Flatpak<br>(F)     | A   | 74S251FC, 74LS251FC                                                                      | 54S251FM, 54LS251FM                                                                         | 4L          |  |

LOGIC SYMBOL

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. defintions

| PIN NAMES                             | DESCRIPTION                               | <b>54/74S (U.L.)</b><br>HIGH/LOW | 54/74LS (U.L.)<br>HIGH/LOW |

|---------------------------------------|-------------------------------------------|----------------------------------|----------------------------|

| S <sub>0</sub> — S <sub>2</sub>       | Select Inputs                             | 1.25/1.25                        | 0.5/0.25                   |

| S <sub>0</sub> — S <sub>2</sub><br>OE | 3-State Output Enable Inputs (Active LOW) | 1.25/1.25                        | 0.5/0.25                   |

| lo — I7                               | Multiplexer Input                         | 1.25/1.25                        | 0.5/0.25                   |

| Z                                     | Multiplexer Output                        | 162/12.5                         | 65/5.0                     |

|                                       |                                           | (50)                             | (25)/(2.5)                 |

| Z                                     | Complementary Multiplexer Output          | 162/12.5<br>(50)                 | 65/5.0<br>(25)/(2.5)       |

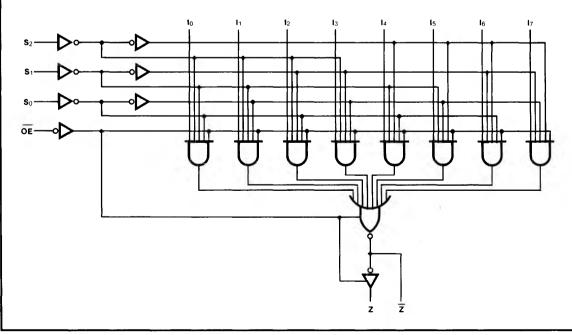

**FUNCTIONAL DESCRIPTION** — This device is a logical implementation of a single-pole, 8-position switch with the switch position controlled by the state of three Select inputs,  $S_0$ ,  $S_1$ ,  $S_2$ . Both assertion and negation outputs are provided. The Output Enable input  $(\overline{OE})$  is active LOW. When it is activated, the logic function provided at the output is:

$$Z = \overline{OE} \bullet (\underbrace{I_0} \bullet \overline{S}_0 \bullet \overline{S}_1 \bullet \overline{S}_2 + I_1 \bullet S_0 \bullet \overline{S}_1 \bullet \overline{S}_2 + I_2 \bullet \overline{S}_0 \bullet S_1 \bullet \overline{S}_2 + I_3 \bullet S_0 \bullet S_1 \bullet \overline{S}_2 + I_4 \bullet \overline{S}_0 \bullet \overline{S}_1 \bullet S_2 + I_5 \bullet S_0 \bullet \overline{S}_1 \bullet S_2 + I_6 \bullet \overline{S}_0 \bullet S_1 \bullet S_2 + I_7 \bullet S_0 \bullet S_1 \bullet S_2)$$

When the Output Enable is HIGH, both outputs are in the high impedance (high Z) state. This feature allows multiplexer expansion by tying the outputs of up to 128 devices together. When the outputs of the 3-state devices are tied together, all but one device must be in the high impedance state to avoid high currents that would exceed the maximum ratings. The Output Enable signals should be designed to ensure there is no overlap in the active LOW portion of the enable voltages.

**TRUTH TABLE**

|    | INP            | UTS            | OUTPUTS        |                                                    |                |

|----|----------------|----------------|----------------|----------------------------------------------------|----------------|

| ŌĒ | S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Z                                                  | Z              |

| Н  | Х              | Х              | Х              | Z                                                  | Z              |

| L  | L              | L              | L              | lo                                                 | 10             |

| L  | L              | L              | Н              | 10 11 12                                           | 11             |

| L  | L              | Н              | L              | Ī2                                                 | 12             |

| L  | L              | Н              | н              | 13<br>14                                           | 13             |

| L  | Н              | L              | L              | 14                                                 | 14             |

| L  | Н              | L              | Н              | Ī <sub>5</sub>                                     | 15             |

|    | н              | Н              | L              | 1 <sub>5</sub><br>1 <sub>6</sub><br>1 <sub>7</sub> | 16             |

| L  | Н              | Н              | Н              | Ī <sub>7</sub>                                     | l <sub>7</sub> |

H = HIGH Voltage Level L = LOW Voltage Level

L = LOW Voltage LevX = ImmaterialZ = High Impedance

#### LOGIC DIAGRAM

### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER  Output Short Circuit Current |             | 54/74S  |      | 54/74LS |      | UNITS | CONDITIONS                                                |

|--------|-----------------------------------------|-------------|---------|------|---------|------|-------|-----------------------------------------------------------|

|        |                                         |             | Min     | Max  | Min     | Max  | J J   |                                                           |

| los    |                                         |             | -40 -10 | -100 | -20     | -100 | mA    | V <sub>CC</sub> = Max                                     |

| Icc    | Power Supply<br>Current                 | Outputs ON  |         |      |         | 10   | mA    | $V_{CC} = Max; I_n, S_n = 4.5 V$<br>$\overline{OE} = Gnd$ |

|        |                                         | Outputs OFF | 1       | 85   | 1       | 12   |       | V <sub>CC</sub> = Max; OE, I <sub>n</sub> = 4.5 V         |

## AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ}\text{C}$ (See Section 3 for waveforms and load configurations)

|                                      |                                           | 54/748                                           | 54/74LS                | _     | CONDITIONS                                                                                  |

|--------------------------------------|-------------------------------------------|--------------------------------------------------|------------------------|-------|---------------------------------------------------------------------------------------------|

| SYMBOL                               | PARAMETER                                 | C <sub>L</sub> = 15 pF<br>R <sub>L</sub> = 280 Ω | C <sub>L</sub> = 15 pF | UNITS |                                                                                             |

|                                      |                                           | Min Max                                          | Min Max                |       |                                                                                             |

| tpLH<br>tpHL                         | Propagation Delay<br>S <sub>n</sub> to Z  | 15<br>13.5                                       | 23<br>33               | ns    | Figs. 3-1, 3-20                                                                             |

| tPLH<br>tPHL                         | Propagation Delay<br>S <sub>n</sub> to Z  | 18<br>19.5                                       | 45<br>30               | ns    | Figs. 3-1, 3-20                                                                             |

| tPLH<br>tPHL                         | Propagation Delay<br>I <sub>n</sub> to Z  | 12<br>12                                         | 28<br>26               | ns    | Figs. 3-1, 3-5                                                                              |

| tPLH<br>tPHL                         | Propagation Delay $I_n$ to $\overline{Z}$ | 7.0<br>7.0                                       | 15<br>15               | ns    | Figs. 3-1, 3-4                                                                              |

| tpzh<br>tpzL                         | Output Enable Time<br>OE to Z or Z        | 19.5<br>21                                       | 20<br>25               | ns    | Figs. 3-3, 3-11, 3-12<br>R <sub>L</sub> = 2 kΩ ('LS251)                                     |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Output Disable Time<br>OE to Z or Z       | 8.5<br>14                                        | 25<br>20               | ns    | Figs. 3-3, 3-11, 3-12<br>$R_L = 2 \text{ k}\Omega \text{ ('LS251)}$<br>$C_L = 5 \text{ pF}$ |