#### **ADVANCE INFORMATION**

### 74LVT646

# 3.3V ABT Octal Transceiver/Register with TRI-STATE® Outputs

#### **General Description**

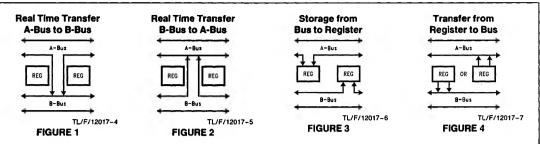

The LVT646 consist of registered bus transceiver circuits, with outputs, D-type flip-flops, and control circuitry providing multiplexed transmission of data directly from the input bus or from the internal storage registers. Data on the A or B bus will be loaded into the respective registers on the LOW-to-HIGH transition of the appropriate clock pin (CPAB or CPBA). The four fundamental handling functions available are illustrated in *Figures 1–4*.

The bus transceivers are designed for low-voltage (3.3V)  $V_{CC}$  applications, but with the capability to provide a TTL interface to a 5V environment. The LVT646 is fabricated with an advanced BiCMOS technology to achieve high speed operation similar to 5V ABT while maintaining a low power dissipation.

#### **Features**

- Input and output interface capability to systems at 5V V<sub>CC</sub>

- Bus-Hold data inputs eliminate the need for external pull-up resistors to hold unused input

- Live insertion/extraction permitted

- Power Up/Down high impedance provides glitch-free bus loading

- Outputs source/sink -32 mA/+64 mA

- Available in SOIC JEDEC, and TSSOP

- Functionally compatible with the 74 series 646

- Latch-up performance exceeds 500 mA

Ordering Code: See Section 11

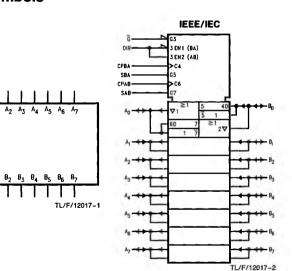

#### **Logic Symbols**

CPAB SAB DIR CPBA SBA

## Connection Diagram Pin Assignment

| for SOIC and TSSOP |    |    |                         |  |  |  |

|--------------------|----|----|-------------------------|--|--|--|

|                    |    |    |                         |  |  |  |

| CPAB —             | 1  | 24 | −v <sub>cc</sub>        |  |  |  |

| SAB-               | 2  | 23 | CPBA                    |  |  |  |

| DIR-               | 3  | 22 | -SBA                    |  |  |  |

| 4 <sub>0</sub> —   | 4  | 21 | <b>−</b> <del>¯</del> ¯ |  |  |  |

| A, —               | 5  | 20 | <b>—</b> в <sub>о</sub> |  |  |  |

| A2 -               | 6  | 19 | <b></b> Β <sub>1</sub>  |  |  |  |

| A3 —               | 7  | 18 | <b>—</b> в <sub>2</sub> |  |  |  |

| A4                 | 8  | 17 | —В <sub>3</sub>         |  |  |  |

| A <sub>5</sub> —   | 9  | 16 | —B₄                     |  |  |  |

| A6 -               | 10 | 15 | —в <sub>5</sub>         |  |  |  |

| A7 —               | 11 | 14 | —8 <sub>6</sub>         |  |  |  |

| GND —              | 12 | 13 | — В <sub>7</sub>        |  |  |  |

|                    |    |    | ľ                       |  |  |  |

|                    |    |    | TL/F/12017-3            |  |  |  |

| Pin Names                      | Description             |  |  |  |

|--------------------------------|-------------------------|--|--|--|

| A <sub>0</sub> -A <sub>7</sub> | Data Register A Inputs  |  |  |  |

| ĺ                              | Data Register A Outputs |  |  |  |

| B <sub>0</sub> -B <sub>7</sub> | Data Register B Inputs  |  |  |  |

|                                | Data Register B Outputs |  |  |  |

| CPAB, CPBA                     | Clock Pulse Inputs      |  |  |  |

| SAB, SBA                       | Transmit/Receive Inputs |  |  |  |

| G                              | Output Enable Input     |  |  |  |

| DIR                            | Direction Control Input |  |  |  |

|                          | SOIC JEDEC                | TSSOP JEDEC  |

|--------------------------|---------------------------|--------------|

| Order Number             | 74LVT646WM<br>74LVT646WMX | 74LVT646MTCX |

| See NS<br>Package Number | M24B                      | MTC24        |

#### Truth Table (Note)

|             | Inputs      |             |             |             |             | Data I/O                       |                                | Function                                                                                                                                                                                                                   |

|-------------|-------------|-------------|-------------|-------------|-------------|--------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G           | DIR         | CPAB        | СРВА        | SAB         | SBA         | A <sub>0</sub> -A <sub>7</sub> | B <sub>0</sub> -B <sub>7</sub> | ranction                                                                                                                                                                                                                   |

| H           | X<br>X<br>X | H or L<br>X | H or L<br>X | X<br>X<br>X | X<br>X<br>X | input                          | Input                          | Isolation<br>Clock A <sub>n</sub> Data into A Register<br>Clock B <sub>n</sub> Data into B Register                                                                                                                        |

| L<br>L<br>L | H<br>H<br>H | X<br>HorL   | X<br>X<br>X | L<br>L<br>H | X<br>X<br>X | Input                          | Output                         | A <sub>n</sub> to B <sub>n</sub> —Real Time (Transparent Mode) Clock A <sub>n</sub> Data into A Register A Register to B <sub>n</sub> (Stored Mode) Clock A <sub>n</sub> Data into A Register and Output to B <sub>n</sub> |

| 1111        | L<br>L<br>L | X<br>X<br>X | X / Hor L   | X<br>X<br>X | L<br>H<br>H | Output                         | Input                          | B <sub>n</sub> to A <sub>n</sub> —Real Time (Transparent Mode) Clock B <sub>n</sub> Data into B Register B Register to A <sub>n</sub> (Stored Mode) Clock B <sub>n</sub> Data into B Register and Output to A <sub>n</sub> |

Note: The data output functions may be enabled or disabled by various signals at the G and DIR inputs. Data input functions are always enabled; i.e., data at the bus pins will be stored on every LOW-to-HIGH transition of the appropriate clock inputs.

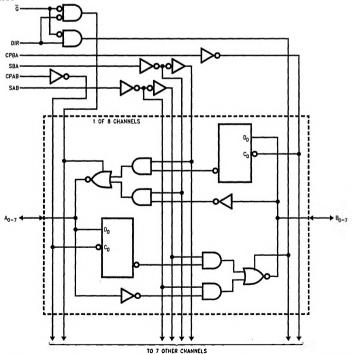

#### **Logic Diagram**

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

TL/F/12017-8