# 9-BIT PARITY GENERATOR AND CHECKER

8262

REFER TO PAGE 15 FOR A, F AND Q PACKAGE PIN CONFIGURATIONS.

# DIGITAL 8000 SERIES TTL/MSI

## **DESCRIPTION**

The 8262 9-Input Parity Generator/Parity Checker is a versatile MSI device commonly used to detect errors in data transmission or in data retrieval. Two outputs (EVEN and ODD) are provided for versatility. An INHIBIT input is provided to disable both outputs of the 8262. (A logic 1 on the INHIBIT input forces both outputs to a logic 0).

When used as a Parity Generator, the 8262 supplies a parity bit which is transmitted together with the data word.

At the receiving end, the 8262 acts as a Parity Checker and indicates that data has been received correctly or that an error has been detected.

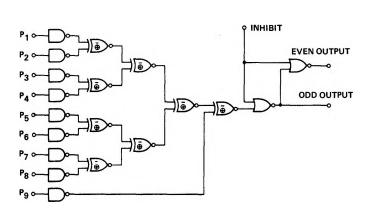

## **LOGIC DIAGRAM**

LOGIC EQUATIONS: Odd =  $P_1 \oplus P_2 \oplus P_3 \oplus P_4 \oplus P_5 \oplus P_6 \oplus P_7 \oplus P_8 \oplus P_9$ Even =  $P_1 \oplus P_2 \oplus P_3 \oplus P_4 \oplus P_5 \oplus P_6 \oplus P_7 \oplus P_8 \oplus P_9$

# **ELECTRICAL CHARACTERISTICS** (Over Recommended Operating Temperature And Voltage)

|                              |      | LIN  | <b>MITS</b> |       | TEST<br>CONDITIONS       |         | OUTPUTS    | NOTES |

|------------------------------|------|------|-------------|-------|--------------------------|---------|------------|-------|

| CHARACTERISTICS              | MIN. | TYP. | MAX.        | UNITS | DATA INPUT<br>UNDER TEST | INHIBIT | UNDER TEST | NOTES |

| "1" Output Voltage           |      |      |             |       |                          |         |            |       |

| Even                         | 2.6  | 3.5  |             | l v   | ٥٧                       | .8V     | -800μA     | 6     |

| Odd                          | 2.6  | 3.5  |             | V     | 2.0V                     | .8V     | −800µA     | 6     |

| "0" Output Voltage           |      |      |             |       |                          |         |            |       |

| Even                         |      |      | 0.40        | l v   | 2.0V                     | .8V     | 16mA       | 7     |

| Odd                          |      |      | 0.40        | V     | ov                       | .8V     | 16mA       | 7     |

| "0" Input Current            |      |      |             |       |                          |         |            | 1     |

| Data Inputs                  | -0.1 |      | -1.6        | mA    | 0.4V                     |         | ļ          | 1     |

| Inhibit                      | -0.1 |      | -3.2        | mA    |                          | 0.4V    |            |       |

| "1" Input Current            |      |      |             |       |                          |         |            |       |

| Data Inputs                  |      |      | 80          | μΑ    | 4.5V                     | }       |            |       |

| Inhibit                      |      | -11- | 160         | μА    |                          | 4.5V    |            |       |

| Input Latch Voltage          |      |      |             |       |                          | t       |            |       |

| Data Inputs                  | 5.5  | 1    |             | V     | 10mA                     | 1       |            | 10    |

| Inhibit                      | 5.5  |      |             | V     |                          | 10mA    |            | 10    |

| Power/Current Consumption    |      |      | 370/70      | mW/mA | 1                        | 1       |            | 11    |

| Output Short Circuit Current |      |      |             |       |                          |         |            |       |

| Even                         | -20  |      | -70         | mA    | ٥v                       | ov      | 0V         |       |

| Odd                          | -20  |      | -70         | mA    | 4.5V                     | ov      | ov         | ]     |

$T_A = 25^{\circ} C$  and  $V_{CC} = 5.0 V$

| CHARACTERISTICS                         |      | LIN  | IITS |       | TEST<br>CONDITIONS | INHIBIT | OUTPUTS    | NOTES |

|-----------------------------------------|------|------|------|-------|--------------------|---------|------------|-------|

| CHARACTERISTICS                         | MIN. | TYP. | MAX. | UNITS | UNDER TEST         |         | UNDER TEST |       |

| Turn-On Times                           |      |      |      |       |                    |         |            |       |

| P <sub>1</sub> - P <sub>8</sub> to Even |      | 35   | 50   | ns    | Pulse              |         |            | 8     |

| P <sub>1</sub> - P <sub>8</sub> to Odd  |      | 30   | 45   | ns    | Pulse              |         |            | 8     |

| P <sub>9</sub> to Even                  |      | 20   | 35   | ns    | Pulse              |         |            | 8     |

| P <sub>9</sub> to Odd                   |      | 15   | 30   | ns    | Pulse              |         |            | 8     |

| Inhibit to Even                         |      | 8    | 15   | ns    |                    | Pulse   |            | 8     |

| Inhibit to Odd                          |      | 8    | 15   | ns    |                    | Pulse   |            | 8     |

| Turn-Off Times                          |      |      |      |       |                    |         | -2         |       |

| P <sub>1</sub> - P <sub>8</sub> to Even |      | 38   | 55   | ns    | Pulse              |         | •          | 8     |

| P <sub>1</sub> - P <sub>8</sub> to Odd  |      | 32   | 45   | ns    | Pulse              |         |            | 8     |

| Pg to Even                              |      | 23   | 40   | ns    | Pulse              |         |            | 8     |

| P <sub>9</sub> to Odd                   |      | 20   | 35   | ns    | Pulse              |         |            | 8     |

| Inhibit to Even                         |      | 10   | 18   | ns    |                    | Pulse   |            | 8     |

| Inhibit to Odd                          |      | 10   | 18   | ns    |                    | Pulse   |            | 8     |

|                                         |      |      |      |       |                    |         |            |       |

#### NOTES:

- 1. All voltage measurements are referenced to the ground terminal. Terminals not specifically referenced are left electrically open.

- 2. All measurements are taken with ground pin tied to zero volts.

- 3. Positive current is defined as into the terminal referenced.

4. Positive logic: "UP" Level = "1", "DOWN" Level = "0".

- 5. Precautionary measures should be taken to ensure current limiting in accordance with Absolute Maximum Ratings should the isolation diodes become forward biased.

- 6. Output source current is supplied through a resistor to ground.

- 7. Output sink current is supplied through a resistor to V<sub>CC</sub>.

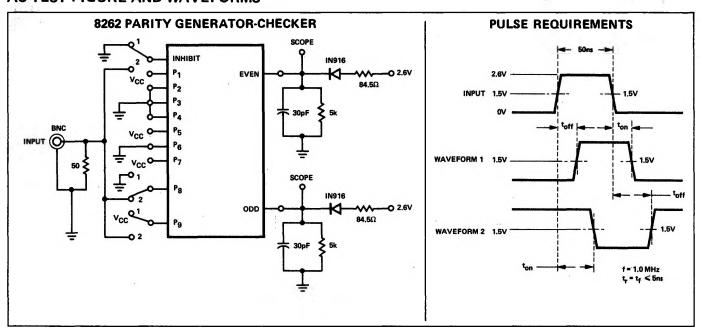

- 8. Refer to AC Test Figure.

- Manufacturer reserves the right to make design and process changes and improvements.

- 10. This test guarantees operation free of input latch-up over the specified operating supply voltage range.

- 11, V<sub>CC</sub> = 5.25 volts.

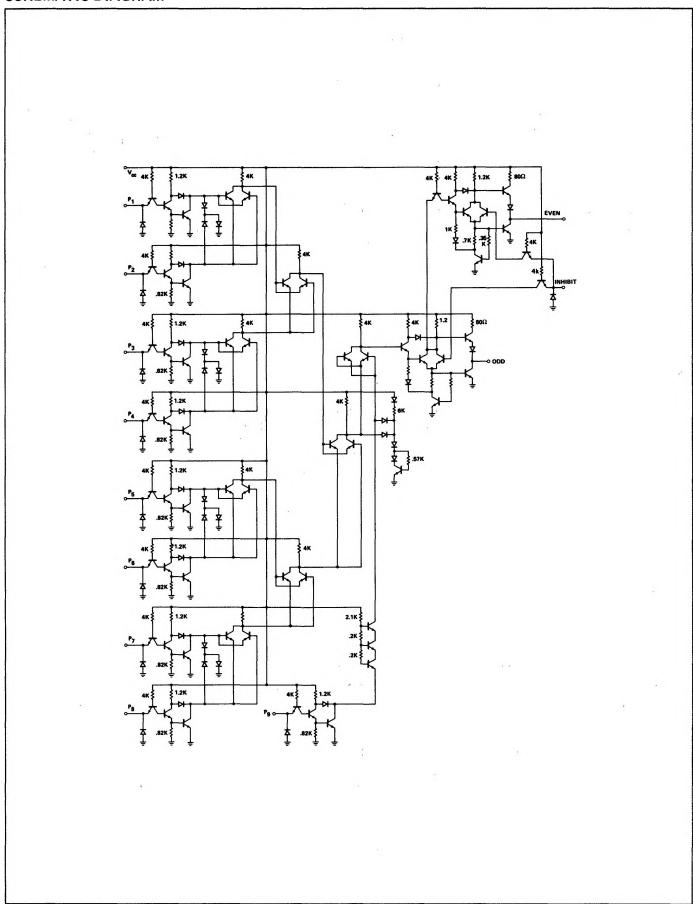

# SCHEMATIC DIAGRAM

# **AC TEST FIGURE AND WAVEFORMS**

## **TRUTH TABLE**

| MEASURE               | SWIT  | SWITCH POSITION |    |      | WAVEFORM |  |

|-----------------------|-------|-----------------|----|------|----------|--|

| DELAY FROM            | 1 INH | P8              | Pg | EVEN | ODD      |  |

| P <sub>8</sub> to ODD | 1     | 2               | 1  |      | 1        |  |

| Pg to ODD             | 1     | 1               | 2  |      | 2        |  |

| Pg to EVEN            | 1     | 2               | 1  | 2    | Ì        |  |

| Pg to EVEN            | 1     | 1               | 2  | 1    |          |  |

| INH to EVEN           | 1 2   | 1 1             | 1  | 2    |          |  |

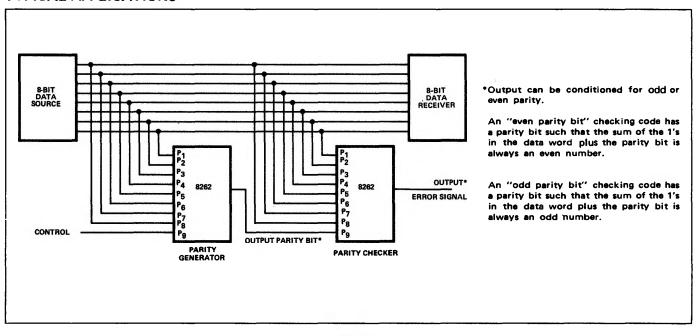

# **TYPICAL APPLICATIONS**