## **TYPES**

8T32 Trl-State, Synchronous User Port

8T33 Open Collector, Synchronous User

8T35 Open Collector, Asynchronous **User Port**

8T36 Tri-State, Asynchronous User Port

## DESCRIPTION

The Addressable I/O Port is an 8-bit bidirectional data register designed to function as an I/O interface element in microprocessor systems. It contains 8 data latches accessible from either a microprocessor port or a user port. Separate I/O control is provided for each port. The 2 ports operate independently, except when both are attempting to input data into the I/O Port. In this case, the user port has priority.

A unique feature of the I/O Port is the way in which it is addressed. Each device has an 8bit. field programmable address, which is used to enable the microprocessor port. When the SC control signal is high, data at the microprocessor port is treated as an address. If the address matches the I/O Port's internally programmed address, the microprocessor port is enabled, allowing data transfer through it.

The port remains enabled until an address which does not match is presented, at which time the port is disabled (data transfer is inhibited). A Master Enable input (ME) can serve as a ninth address bit, allowing 512 I/O Ports to be individually selected on a bus, without decoding. The user port is accessible at all times, independent of whether or not the microprocessor port is selected.

A unique feature of this family is their ability to start up in a predetermined state. If the clock is maintained at a voltage less than .8V until the power supply reaches 3.5V, the user port will always be all logic 1 levels, while the port will be all logic 0 levels.

## ORDERING

The 8T32/33/35/36 may be ordered in preaddressed form. To order a preaddressed device use the following part number format:

N8TYY-XXX P -P = F Ceramic package NA Plastic package XXX = Any address from 000 through 255 (decimal) -256 available addresses -YY = I/O Port version (32, 33, 35, 36)

A stock of 8T32s and 8T36s with addresses 1 through 10 will be maintained. A small quantity of addresses 11 through 50 will also be available with a longer lead time.

## **FEATURES**

- A field-programmable address allows 1 of 512 I/O Ports on a bus to be selected, without decoders.

- Each device has 2 ports, one to the user, the other to a microprocessor.

- Completely bidirectional.

- Ports are independent, with the user port having priority for data entry.

- A selected I/O Port de-selects itself when another I/O Port address is sensed.

- User data input available as synchronous (8T32, 8T33) or as asynchronous (8T35, 8T36) function.

- . The user data bus is available with tristate (8T32, 8T36) or open collector (8T33, 8T35) outputs.

- At power up, the I/O Port is not selected and the user port outputs are high.

- . Tri-state TTL outputs for high drive capa-

- Directly compatible with the 8X300 Microcontroller.

- Operates from a single 5V power supply over a temperature range of 0°C to 70°C.

## PIN CONFIGURATION

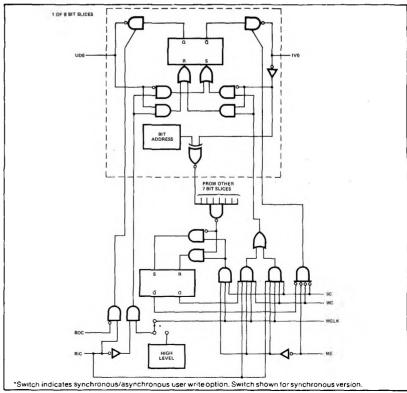

## **BLOCK DIAGRAM**

## PIN DESCRIPTION

| PIN   | SYMBOL                     | NAME AND FUNCTION                                                                                                                                                                                     | TYPE                      |

|-------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 1-8   | UD0-UD7:                   | User Data I/O Lines. Bidirectional data lines to communicate with user's equipment. Either tristate or open collector outputs are available.                                                          | Active high               |

| 16-23 | Ī <b>V</b> Ō- <b>ĪV</b> 7: | Microprocessor Bus. Bidirectional data lines to communicate with controlling digital system (microprocessor).                                                                                         | Active low<br>three-state |

| 10    | BIC:                       | Input Control. User input to control writing into the I/O Port from the user data lines.                                                                                                              | Active low                |

| 9     | BOC:                       | Output Control. User input to control reading from the I/O Port onto the user data lines.                                                                                                             | Active low                |

| 11    | ME:                        | Master Enable. System input to enable or dis-<br>able all other system inputs and outputs.<br>It has no effect on user inputs and outputs.                                                            | Active low                |

| 15    | WC:                        | Write Command. When WC is high and SC is low, I/O Port, if selected, stores contents of IVO-IV7 as data.                                                                                              | Active high               |

| 14    | SC:                        | Select Command. When SC is high and WC is low, data on IV0-IV7 is interpreted as an address. I/O Port selects itself if its address is identical to $\mu$ P bus data; it de-selects itself otherwise. | Active high               |

| 13    | MCLK:                      | Master Clock. Input to strobe data into the latches. See function tables for details.                                                                                                                 | Active high               |

| 24    | VCC:                       | 5V power connection.                                                                                                                                                                                  |                           |

| 12    | GND:                       | Ground.                                                                                                                                                                                               |                           |

| BIC |     |      | USER DATA BUS FUNCTION |             |  |  |

|-----|-----|------|------------------------|-------------|--|--|

| BIC | вос | MCLK | 8T32, 8T33             | 8T35, 8T36  |  |  |

| Н   | L   | Х    | Output Data            | Output Data |  |  |

| L   | ) x | Н    | Input Data             | Input Data  |  |  |

| L   | ) x | L    | Inactive               | Input Data  |  |  |

| Н   | Н   | X    | Inactive               | Inactive    |  |  |

H = High Level L = Low Level X = Don't care

Table 1 USER PORT CONTROL FUNCTION

| ME | sc | wc | MCLK     | BIC | STATUS<br>LATCH | I/O PORT<br>FUNCTION   |

|----|----|----|----------|-----|-----------------|------------------------|

| L  | L  | L  | X        | X   | SET             | Output Data            |

| L  | L  | н  | н        | ) н | SET             | Input Data             |

| L  | Н  | L  | н        | X   | X               | Input Address          |

| L  | Н  | Н  | н        | L   | ×               | Input Address          |

| L  | ∖н | н  | \ н      | Н   | ×               | Input Data and Address |

| L  | X  | н  | <u> </u> | X   | l x             | Inactive               |

| L  | Н  | X  | L        | X   | ) ×             | Inactive               |

| L  | L  | Н  | н        | L   | X               | Inactive               |

| L  | L  | X  | X        | ) x | Not Set         | Inactive               |

| Н  | X  | Х  | X        | X   | ×               | Inactive               |

Table 2 MICROPROCESSOR PORT CONTROL FUNCTION

# **USER DATA BUS CONTROL**

The activity of the user data bus is controlled by the BIC and BOC inputs as shown in Table 1.

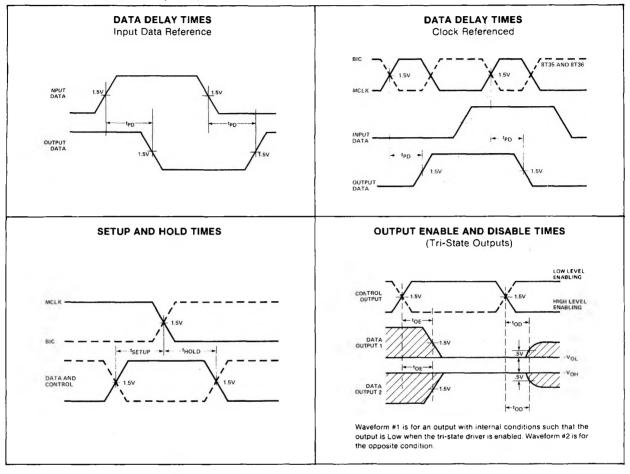

For the 8T32 and 8T33, user data input is a synchronous function with MCLK. A low level on the BIC input allows data on the user data bus to be written into the data latches only if MCLK is at a high level. For the 8T35 and 8T36, user data input is an asynchronous function. A low level on the BIC input allows data on the user data bus to be latched regardless of the level of the MCLK input. Note that when 8T35 or 8T36 are used with the 8X300 Microcontroller care must be taken to insure that the Microprocessor bus is stable when it is being read by the 8X300 Microcontroller.

To avoid conflicts at the Data Latches, input from the Microprocessor Port is inhibited when BIC is at a low level. Under all other conditions the 2 ports operate independently.

## MICROPROCESSOR BUS CONTROL

As is shown in Table 2, the activity of the microprocessor port is controlled by the ME, SC, WC and BIC inputs, as well as the state of an internal status latch. BIC is included to show user port priority over the microprocessor port for data input.

Each I/O Port's status latch stores the result of the most recent I/O Port select; it is set when the I/O Port's internal address matches the Microprocessor Bus. It is cleared when an address that differs from the internal address is presented on the Microprocessor Bus.

In normal operation, the state of the status latch acts like a master enable; the micro-processor port can transfer data only when the status latch is set.

When SC and WC are both high, data on the Microprocessor Bus is accepted as data, whether or not the I/O Port was selected. The data is also interpreted as an address. The I/O Port sets its select status if its address matches the data read when SC and WC were both high; it resets its select status otherwise.

## **BUS OPERATION**

Data written into the I/O Port from one port will appear inverted when read from the other port. Data written into the I/O Port from one port will not be inverted when read from the same port.

# AC ELECTRICAL CHARACTERISTICS $0^{\circ}C \le T_A \le 70^{\circ}C$ , $V_{CC} = 5V \pm 5\%$

|                  |                          |                   | TEST                  |                                  |                |                |      |

|------------------|--------------------------|-------------------|-----------------------|----------------------------------|----------------|----------------|------|

| PA               | RAMETER                  | INPUT             | CONDITION             | Min                              | Тур            | Max            | UNIT |

| t <sub>PD</sub>  | User data delay (Note 1) | MCFK.<br>MCFK.    | C <sub>L</sub> = 50pF |                                  | 25<br>45<br>40 | 38<br>61<br>55 | ns   |

| <sup>†</sup> OE  | User output enable       | BOC               | C <sub>L</sub> = 50pF | 18                               | 26             | 47             | ns   |

| top              | User output disable      | BIC<br>BOC        | C <sub>L</sub> = 50pF | 18<br>16                         | 28<br>23       | 35<br>33       | ns   |

| t <sub>PD</sub>  | μP data delay (Note 1)   | IVBX<br>MCLK      | C <sub>L</sub> = 50pF |                                  | 38<br>48       | 53<br>61       | ns   |

| <sup>t</sup> OE  | μP output enable         | ME<br>SC<br>WC    | C <sub>L</sub> = 50pF | 14                               | 19             | 25             | ns   |

| t <sub>OD</sub>  | μP output disable        | ME<br>SC<br>WC    | C <sub>L</sub> = 50pF | 13                               | 17             | 32             | ns   |

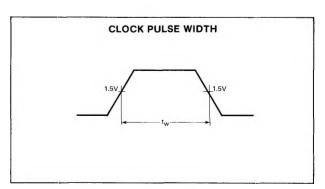

| t <sub>W</sub>   | Minimum pulse width      | MCLK<br>BIC†      |                       | 40<br>35                         |                | 8              | ns   |

| <sup>t</sup> SET | UP Minimum setup time    | BIC* IVX ME SC WC | (Note 2)              | 15<br>25<br>55<br>30<br>30<br>30 |                |                | ns   |

| <sup>t</sup> HOL | D Minimum hold time      | BIC. INX WE SC MC | (Note 2)              | 25<br>10<br>10<br>5<br>5         |                |                | ns   |

<sup>&#</sup>x27; Applies for 8T32 and 8T33 only

## NOTES

<sup>†</sup> Applies for 8T35 and 8T36 only.

Times are referenced to MCLK for 8T32 and 8T33, and are referenced to BIC for 8T35 and 8T36.

Data delays referenced to the clock are valid only if the input data is stable at the arrival

of the clock and the hold time requirement is met.

Set up and hold times given are for "normal" operation. BIC setup and hold times are

for a user write operation. SC setup and hold times are for an I/O Port select operation.

WC setup and hold times are for an Microprocessor Bus write operation. ME setup and

hold times are for both IV write and select operations.

# DC ELECTRICAL CHARACTERISTICS $0^{\circ}$ C $\leq$ T $_{A} \leq$ 70 $^{\circ}$ C, V $_{CC}$ = 5V ± 5%

|                 | PARAMETER                                                     | TEST CONDITIONS                                    | LIMITS   |      |      | UNITS    |

|-----------------|---------------------------------------------------------------|----------------------------------------------------|----------|------|------|----------|

|                 | I ARAWE I ER                                                  | 1231 CONDITIONS                                    | Min      | Тур  | Max  |          |

| V <sub>IH</sub> | High-level input voltage                                      |                                                    | 2.0      |      |      | V        |

| VIL             | Low-level input voltage                                       |                                                    |          |      | .8   | V        |

| V <sub>CL</sub> | Input clamp voltage                                           | I <sub>I</sub> = -5mA                              |          |      | -1   | V        |

| Ін              | High-level input current <sup>1</sup>                         | $V_{CC} = 5.25V$<br>$V_{IH} = 5.25V$               |          | <10  | 100  | μА       |

| liL             | Low level input current1                                      | $V_{CC} = 5.25V$ $V_{IL} = .5V$                    |          | -350 | -550 | μА       |

| VOL             | Low-level output voltage                                      | V <sub>CC</sub> = 4.75V<br>I <sub>OL</sub> = 16mA  |          |      | .55  | V        |

| Vон             | High-level output voltage                                     | $V_{CC} = 4.75V$ $I_{OH} = -3.2$ mA                | 2.4      |      |      | V        |

| los             | Short-circuit output current <sup>2</sup><br>UD bus<br>IV bus | V <sub>CC</sub> = 4.75V<br>V <sub>CC</sub> = 4.75V | 10<br>20 |      |      | mA<br>mA |

| lcc             | Supply current                                                | V <sub>CC</sub> = 5.25V                            |          | 100  | 150  | mA       |

#### NOTES

- The input current includes the Tri-state/Open Collector leakage current of the output driver on the data lines.

- 2. Only one output may be shorted at a time.

- 3. These limits do not apply during address programming.

# Absolute Maximum Ratings:

Input voltage<sup>3</sup> ..... 5.5V

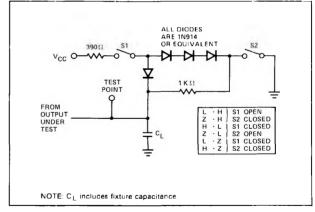

# TEST LOAD CIRCUIT (OPEN COLLECTOR OUTPUTS)

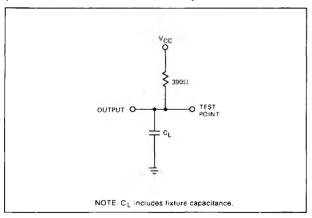

# TEST LOAD CIRCUIT (TRI-STATE OUTPUTS)

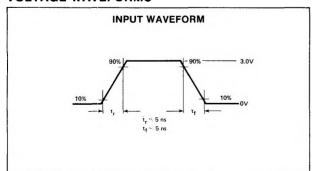

## **VOLTAGE WAVEFORMS**

# VOLTAGE WAVEFORMS (Cont'd)

## ADDRESS PROGRAMMING

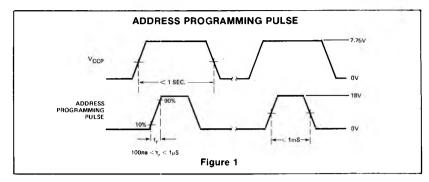

The I/O Port is manufactured such that an address of all high levels (>2V) on the Microprocessor Bus inputs matches the Port's internal address. To program a bit so a low-level input (<0.8V) matches, the following procedure should be used:

- Set all control inputs to their inactive state (BIC = BOC = ME = V<sub>CC</sub>, SC = WC = MCLK = GND). Leave all Microprocessor Bus I/O pins open.

- 2. Raise VCC to 7.75V ± .25V.

- After V<sub>CC</sub> has stabilized, apply a single programming pulse to the user data bus bit where a low-level match is desired. The voltage should be limited to 18V; the current should be limited to 75mA. Apply the pulse as shown in Figure 1.

- 4. Return V<sub>CC</sub> to 0V. (Note 1).

- 5. Repeat this procedure for each bit where a low-level match is desired.

- Verify that the proper address is programmed by setting the Port's status latch (IV0-IV7 = desired address, ME = WC = L, SC = MCLK = H). If the proper address has been programmed, data presented at the μP bus will appear inverted on the user bus outputs. (Use normal V<sub>CC</sub> and input voltage for verification.)

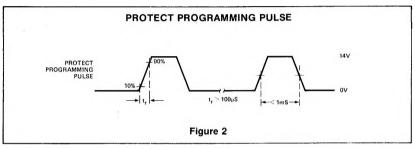

After the desired address has been programmed, a second procedure must be followed to isolate the address circuitry. The procedure is:

- Set V<sub>CC</sub> and all control inputs to 0V. (V<sub>CC</sub> = BIC = BOC = ME = SC = WC = MCLK = 0V). Leave all Microprocessor Bus I/O pins open.

- Apply a protect programming pulse to every user data bus pin, one at a time. The voltage should be limited to 14V; the current should be limited to 150mA. Apply the pulse as shown in Figure 2.

- 3. Verify that the address circuitry is isolated by applying 7V to each user data bus pin and measuring less than 1mA of input current. The conditions should be the same as in step 1 above. The rise time on the verification voltage must be slower than 100us.

## PROGRAMMING SPECIFICATIONS<sup>1</sup>

|                  |                                                   | TEST                    | LIMITS       |     |              |          |

|------------------|---------------------------------------------------|-------------------------|--------------|-----|--------------|----------|

|                  | PARAMETER                                         | CONDITIONS              | Min          | Тур | Max          | UNITS    |

| V <sub>CCP</sub> | Programming supply voltage<br>Address<br>Protect  |                         | 7.5          | 0   | 8.0          | V<br>V   |

| ICCP             | Programming supply current                        | V <sub>CCP</sub> = 8.0V |              |     | 250          | mA       |

|                  | Max time V <sub>CCP</sub> > 5.25V                 |                         |              |     | 1.0          | s        |

|                  | Programming voltage<br>Address<br>Protect         |                         | 17.5<br>13.5 |     | 18.0<br>14.0 | v<br>v   |

|                  | Programming current<br>Address<br>Protect         |                         |              |     | 75<br>150    | mA<br>mA |

|                  | Programming pulse rise time<br>Address<br>Protect |                         | .1<br>100    |     | 1            | μs<br>μs |

|                  | Programming pulse width                           |                         | .5           |     | 1            | ms       |

NOTE

<sup>1.</sup> If all programming can be done in less than 1 second, VCC may remain at 7.75V for the entire programming cycle

# **APPLICATIONS**

Figure 3 shows some of the various ways to use the I/O Port in a system. By controlling the BIC and BOC lines, the device may be used for the input and output of data, control, and status signals. I/O Port 1 functions bidirectionally for data transfer and I/O Port 2 provides a similar function for discrete status and control lines. I/O Ports 3 and 4 serve as dedicated output and input ports, respectively.