### 96LS32

# ADDRESS MULTIPLEXER/REFRESH COUNTER (For 4K Dynamic RAMs)

DESCRIPTION — The 96LS32 is an address multiplexer and refresh counter for multiplexed address dynamic RAMs requiring refresh of up to six input addresses (or 4K bits for 64 x 64 organization). It multiplexes 12 bits of system applied address to six output address pins. The device also contains a 6-bit refresh counter which is externally clocked so that either distributed or burst refresh may be used. The high performance of the 96LS32 makes it especially suitable for use with high speed n-channel RAMs like the M4027. The 96LS32 operates from a single +5.0 V power supply and is specified for operation over

- SIMPLIFIES SYSTEM DESIGN

- REDUCES PACKAGE COUNT

- DRIVES HIGH CAPACITANCE LOADS

a 0°C to +75°C ambient temperature range.

- USE FOR DISTRIBUTED OR BURST REFRESH

- STANDARD 24-PIN DUAL IN-LINE PACKAGE

- LOW POWER SCHOTTKY DESIGN MINIMIZES POWER CONSUMPTION

**ORDERING CODE:** See Section 9

| PKGS               | PIN<br>OUT | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                           | PKG<br>TYPE |

|--------------------|------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------|

|                    |            | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$ $T_A = -55^{\circ}\text{C to} + 125^{\circ}\text{C}$ |             |

| Plastic<br>DIP (P) | Α          | 96LS32PC                                                                                 |                                                                                          | 9N          |

| Ceramic<br>DIP (D) | Α          | 96LS32DC                                                                                 | 96LS32DM                                                                                 | 6N          |

| Flatpak<br>(F)     | Α          | 96LS32FC                                                                                 | 96LS32FM                                                                                 | 4M          |

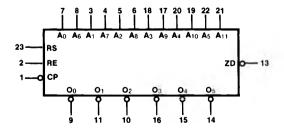

## CONNECTION DIAGRAM PINOUT A

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                                                    | DESCRIPTION                                     | <b>96XX (U.L.)</b><br>HIGH/LOW |  |

|--------------------------------------------------------------|-------------------------------------------------|--------------------------------|--|

| A <sub>0</sub> — A <sub>5</sub>                              | Row Address Inputs                              | 0.5/0.13                       |  |

| $A_6 - A_{11}$                                               | Column Address Inputs                           | 0.5/0.13                       |  |

| CP                                                           | Clock Pulse Input (Active Falling Edge)         | 0.5/0.13                       |  |

| RE                                                           | Refresh Enable Input (Active HIGH)              | 0.5/0.13                       |  |

| RS                                                           | Row Select Input (Active HIGH)                  | 0.5/0.13                       |  |

| ZD                                                           | Refresh Counter Zero Detect Output (Active LOW) | 25/3.1                         |  |

| $\frac{RS}{\overline{ZD}}$ $\overline{O}_0 - \overline{O}_5$ | Address Outputs                                 | 25/3.1                         |  |

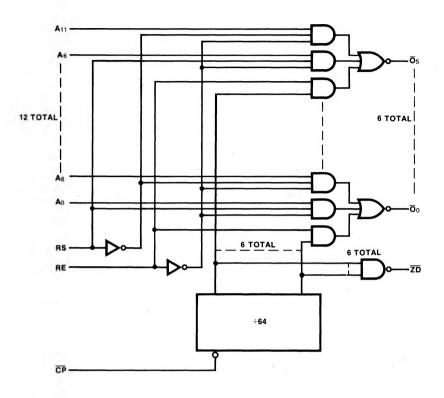

#### LOGIC DIAGRAM

#### LOGIC SYMBOL

V<sub>CC</sub> = Pin 24 GND = Pin 12 **FUNCTIONAL DESCRIPTION**—The 96LS32 address multiplexer/refresh counter performs the following functions:

- 1. Row, Column and Refresh Address multiplexing

- 2. Address counting for burst or distributed refresh

These functions are controlled by two signals, Refresh Enable and Row Select, both of which are active HIGH TTL inputs, the Function Table shows the levels required to multiplex to the output:

- 1. Refresh address (from internal counter)

- 2. Row addresses (A<sub>0</sub> through A<sub>5</sub>)

- 3. Column addresses (A6 through A11)

BURST REFRESH MODE—When refresh is requested the Refresh Enable input is HIGH. This input is ANDed with the six outputs of the internal 6-bit counter. At each  $\overline{CP}$  pulse the counter increments by one, sequencing the outputs  $(\overline{O_0} - \overline{O_5})$  through all 64 row addresses. When the counter sequences to all zeroes, the Zero Detect output goes LOW signaling the end of the refresh sequence. Due to counter decoding spikes, the Zero Detect output is valid only after  $t_{CZ}$  following the LOW going edge of  $\overline{CP}$ .

DISTRIBUTED REFRESH MODE—In the distributed refresh mode, one row is selected for refresh each  $(t_{refresh/n})$  time where n = number of rows in the device and refresh is the specified refresh rate for the device. For the M4027,  $t_{refresh} = 2.0$  ms and n = 64, therefore one row is refreshed each 31  $\mu$ s. Following the refresh cycle at row n, the  $\overline{CP}$  input is pulsed, advancing the refresh address by one row so that the next refresh cycle will be performed on row n + 1. The  $\overline{CP}$  input may be pulsed following each refresh cycle or within the refresh cycle after the specified memory device address hold time.

ROW AND COLUMN ADDRESS — All twelve system address lines are applied to the inputs of the 96LS32. When Refresh Enable is LOW and Row Select is HIGH, the input addresses  $A_0 - A_5$  are gated to the outputs and applied to the driven memories. Conversely, when Row Select is LOW (with Refresh Enable still LOW), input addresses  $A_6 - A_{11}$  are gated to the outputs and applied to the driven memories. When memory devices are driven directly by the 96LS32, the address applied to the memory devices is the inverse of the address at the inputs due to the inverted outputs of the 96LS32. This should be remembered when checking out the memory system.

#### **FUNCTION TABLE**

| Refresh<br>Enable | Row<br>Select | Outputs                                                          |

|-------------------|---------------|------------------------------------------------------------------|

| Н                 | Х             | Refresh Address (from internal counter)                          |

| L                 | Н             | Row Address (complement of A <sub>0</sub> — A <sub>5</sub> )     |

| L                 | L             | Column Address (complement of A <sub>6</sub> — A <sub>11</sub> ) |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial