# HD44790, HD44795 (LCD-III)

AUTOMOTIVE

4-Bit CMOS Microcomputer

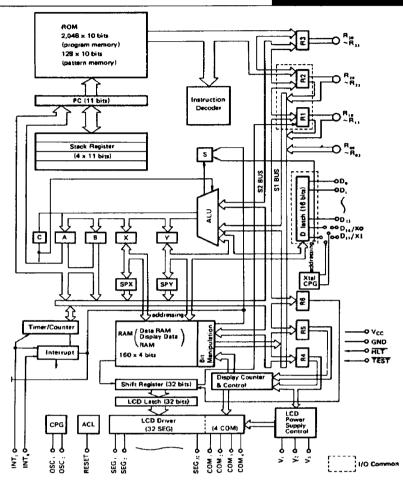

The LCD-III is the CMOS 4-bit single chip microcomputer which contains ROM, RAM, I/O, Timer/Event Counter and Control Circuit, Direct Drive Circuit for LCD on single chip. The LCD-III is designed to drive LCD directly and perform efficient controller function as well as arithmetic function for both binary and BCD data. With the on-chip crystal oscillator for timer, the clock function is easily realized. The CMOS technology of the LCD-III provides the flexibility of microcomputers for battery powered and battery back-up applications in combination with low power consuming LCD.

- **FEATURES**

- 4-bit Architecture

- 2,048 Words of Program ROM (10 bits/Word)

- 128 Words of Pattern ROM (10 bits/Word)

160 Digits of Data RAM and Display Data RAM (4 bits/ Digit)

- Control Circuit and Direct Drive Circuit for LCD

- 4 Commons (Duty Radio; Static, 1/2, 1/3, 1/4)

- 32 Segments (Externally expandable up to 96 Segments using external Drivers HD44100s)

- 32 I/O Lines and 2 External Interrupt Lines

- Timer/Event Counter

- All Instructions except One Instruction; Single Word and Single Cycle

- **BCD** Arithmetic Instructions

- Pattern Generation Instruction

- Table Look Up Capability

- Powerful Interrupt Function

- 3 Interrupt Sources

- 2 External Interrupt Lines

Timer/Event Counter

- Multiple Interrupt Capability

- Bit Manipulation Instructions for Both RAM and I/O

- Option of I/O Configuration Selectable on Each Pin; Pull Up MOS or CMOS or Open Drain

- Built-in Oscillator for System Clock (Resistor or Ceramic Filter)

- **Built-in Crystal Oscillator for Timer**

- **Built-in Power-on Reset Circuit**

186

- Low Operating Power Dissipation; 2mW typ.

- Stand-by Mode (Halt Mode); 50µW max.

- 2 Versions; HD44790 VCC = 5V ± 10%, 10 μs Instruction Cycle Time

HD44795 VCC = 2.7V to 5.5V, 20 μs Instruc-tion Cycle Time

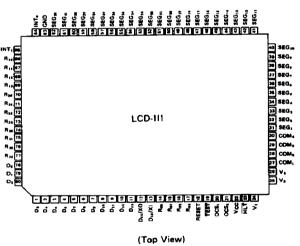

PIN ARRANGEMENT

Data Sheets contain information for automotive operation only. Refer to Reference Guide (Section 9) for a listing of supplementary publications which provide complete specifications.

Hitachi America Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

# LCD-III (HD44790, HD44795)

# **AUTOMOTIVE VERSION**

- HD44790 ELECTRICAL CHARACTERISTICS (VCC=5V±10%)

- ABSOLUTE MAXIMUM RATINGS

| ltem                             | Symbol            | Value                        | Unit | Note                                                                 |

|----------------------------------|-------------------|------------------------------|------|----------------------------------------------------------------------|

| Supply Voltage                   | Vcc               | -0.3 to +7.0                 | V    |                                                                      |

| Pin Voltage (1)                  | V <sub>T1</sub>   | -0.3 to V <sub>CC</sub> +0.3 | V    | Applied to all pins except those specified in V <sub>T2</sub> .      |

| Pin Voltage (2)                  | V <sub>T2</sub>   | 0.3 to +10.0                 | v    | Applied to open-drain output pins<br>and open-drain I/O common pins. |

| Maximum Total Output Current (1) | -ΣI <sub>α1</sub> | 45                           | mA   | (Note 3)                                                             |

| Maximum Total Output Current (2) | ΣΙ <sub>ο2</sub>  | 45                           | mA   | (Note 3)                                                             |

| Operating Temperature            | Topr              | -40 to +85                   | °c   |                                                                      |

| Storage Temperature              | T <sub>eto</sub>  | -55 to +125                  | °c   |                                                                      |

- (NOTE) 1. Permanent LSt demage may occur if maximum ratings are exceeded.

Normal operation should be under the conditions of "ELECTRICAL CHARACTERISTICS-1, -2." If these conditions are exceeded, it could be cause of malfunction of LSI and affects reliability of LSI.

2. All voltages are with respect to GND.

3. Maximum Total Output Current is the total sum of output currents which can flow out or in simultaneously.

4. Power supply condition V<sub>CC</sub> ≥ V1 ≥ V2 ≥ V3 ≥ GND should be maintained.

# **@HITACHI**

Hitachi America Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

# • ELECTRICAL CHARACTERISTICS - 1 (V<sub>CC</sub> =5V±10%, T<sub>8</sub> =-40 to +85°C)

| ltem                                     | Symbol Test Conditions |                                                                                                                                                                |                                        | Value                            |        | Unit | Note |          |

|------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------|--------|------|------|----------|

| iteni                                    |                        |                                                                                                                                                                |                                        | min                              | typ    | max  |      | _        |

| Input "Low" Voltage                      | VIL                    |                                                                                                                                                                |                                        |                                  |        | 1.0  |      | (0)      |

| Input "High" Voltage (1)                 | V <sub>IH1</sub>       |                                                                                                                                                                |                                        | V <sub>CC</sub> -1.0             |        | Vcc  |      | (9)      |

| Input "High" Voltage (2)                 | V <sub>IH2</sub>       |                                                                                                                                                                |                                        | V <sub>cc</sub> -1.0             |        | 10   | ٧    | (10)     |

| Output "Low" Voltage                     | VoL                    | I <sub>OL</sub> = 1.6 mA                                                                                                                                       |                                        | 2.4                              |        | 0.8  | V    |          |

| Output "High" Voltage (1)                | V <sub>OH1</sub>       |                                                                                                                                                                | -I <sub>OH</sub> = 1.0 mA              |                                  |        |      | ٧    | (1)      |

| Output "High" Voltage (2)                | V <sub>OH2</sub>       |                                                                                                                                                                | -I <sub>OH</sub> = 0.01 mA             |                                  |        |      | V    | (2)      |

| Driver Voltage Descending (COM)          | V <sub>d</sub> ,       | ld = 0.05 mA                                                                                                                                                   |                                        | -                                |        | 0.4  | ٧    | (13)     |

| Driver Voltage Descending (SEG)          | V <sub>d</sub>         | ld = 0.01 mA                                                                                                                                                   |                                        |                                  |        | 0.4  | ٧    | (13)     |

| Dividing Resistor of LCD Power<br>Supply | Rwell                  |                                                                                                                                                                |                                        | 25                               | _      | 300  | kΩ   | (4.5)    |

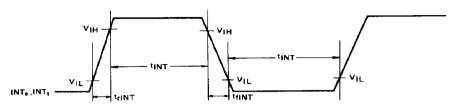

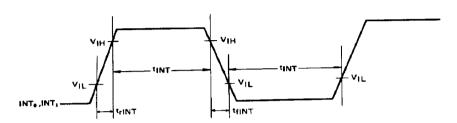

| Interrupt Input Hold Time                | tINT                   |                                                                                                                                                                |                                        | 2 - T <sub>inst</sub>            |        |      | μs   | (15)     |

| Interrupt Input Fall Time                | trint                  |                                                                                                                                                                |                                        |                                  |        | 50   | μs   | (15)     |

| Interrupt Input Rise Time                | trINT                  |                                                                                                                                                                |                                        |                                  |        | 50   | μs   | (15)     |

| Output "High" Current                    | Тон                    | V <sub>OH</sub> = 10V                                                                                                                                          |                                        |                                  |        | 3    | μА   | (3)      |

| Input Leakage Current                    | l <sub>1</sub> L       | $V_{in} = 0$ to $V_{CC}$                                                                                                                                       |                                        |                                  |        | 1.0  | μА   | (3), (9) |

| Input Leakage Current                    | '1"                    | V <sub>in</sub> = 0 to 10V                                                                                                                                     |                                        |                                  |        | 3    |      | (3), (10 |

| Pull up MOS Current                      | -lp                    | V <sub>CC</sub> = 5V                                                                                                                                           |                                        | 45                               |        | 250  | μΑ   | ļ        |

| Supply Current (1)                       | I <sub>CC1</sub>       | V <sub>in</sub> = V <sub>CC</sub> , V <sub>C</sub><br>Ceramic Filter<br>(f <sub>osc</sub> = 400 kH:                                                            |                                        | _                                | -      | 1.3  | mA   | (5)      |

| Supply Current (2)                       | lc€2                   | V <sub>in</sub> = V <sub>CC</sub> , V <sub>C</sub><br>R <sub>f</sub> Oscillation<br>(f <sub>osc</sub> = 400 kH<br>External Clock<br>(f <sub>cp</sub> = 400 kHz | z)<br>(Operation                       | _                                | _      | 0.6  | mA   | (5), (12 |

|                                          | 1.                     |                                                                                                                                                                | V <sub>in</sub> = 0 to V <sub>CC</sub> | _                                | -      | 1.0  | μΑ   | (6), (9) |

| Standby I/O Leakage Current              | ILS                    | HL1=1.0V                                                                                                                                                       | V <sub>in</sub> = 0 to 10V             | _                                | _      | 3    | μΑ   | (6),(10  |

| Standby Supply Current (1)               | I <sub>CCS1</sub>      | Vin = VCC, HLT = 0.2V                                                                                                                                          |                                        |                                  |        | 10   | μΑ   | (11)     |

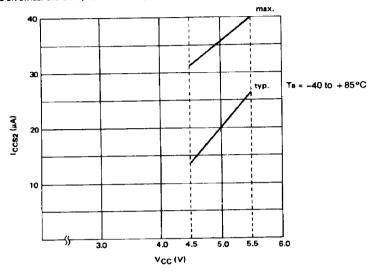

| Standby Supply Current (2)               | I <sub>CCS2</sub>      | Vin = Vcc, HL                                                                                                                                                  | .T ≠ 0.2V                              |                                  |        | 40   | μΑ   | (7)      |

| Frame Frequency of LCD Drive             | f <sub>F</sub>         | n=1 (static)<br>n=2 (1/2 Duty)<br>n=3 (1/3 Duty)<br>n=4 (1/4 Duty)                                                                                             |                                        | 1<br>256 x n x T <sub>inst</sub> |        |      | Hz   |          |

| LCD Display Voltage                      | V <sub>LCD</sub>       | V <sub>CC</sub> -V <sub>3</sub>                                                                                                                                |                                        | 2.5                              |        | Vcc  | V    | (8)      |

| External Clock Operation; System         |                        |                                                                                                                                                                |                                        | ·                                | 1      |      |      |          |

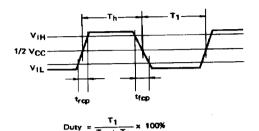

| External Clock Frequency                 | fcp                    | T                                                                                                                                                              |                                        | 40                               | 400    | 440  | kHz  |          |

| External Clock Duty                      | Duty                   |                                                                                                                                                                |                                        | 45                               | 50     | 55   | %    |          |

| External Clock Rise Time                 | t <sub>rep</sub>       |                                                                                                                                                                |                                        | 0                                | _      | 0.2  | μs   |          |

| External Clock Fall Time                 | t <sub>fop</sub>       | 1                                                                                                                                                              |                                        | 0                                | _      | 0.2  | μs   |          |

| Instruction Cycle Time                   | Tinst                  | T <sub>inst</sub> = 4/ <sub>fcp</sub>                                                                                                                          |                                        | 9.1                              | 10     | 100  | μs   |          |

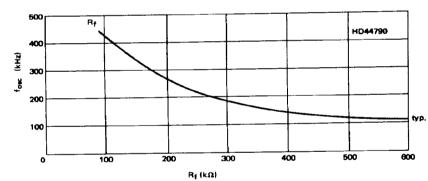

| Internal Clock Operation (Rf Oscil       |                        |                                                                                                                                                                |                                        |                                  |        |      |      |          |

| Clock Oscillation Frequency              | fosc                   | $R_f = 110k\Omega \pm 3$                                                                                                                                       | <u> </u>                               | 300                              |        | 500  | kHz  |          |

| Instruction Cycle Time                   | Tinst                  | Tinst = 4/fasc                                                                                                                                                 |                                        | 8.0                              | -      | 13.3 | μs   |          |

| Internal Clock Operation (Ceramic        |                        | ation); System Ck                                                                                                                                              | ock                                    |                                  |        |      |      |          |

| Clock Oscillation Frequency              | fosc                   | Ceramic Filter                                                                                                                                                 |                                        | 392                              |        | 408  | kHz  | <u> </u> |

| Instruction Cycle Time                   | Tinst                  | Tinst = 4/fosc                                                                                                                                                 |                                        | 9.8                              |        | 10.2 | μs   |          |

| Internal Clock Operation (Crystal (      |                        |                                                                                                                                                                |                                        |                                  |        |      |      |          |

| Clock Oscillation Frequency              | forex                  | Crystal                                                                                                                                                        |                                        |                                  | 32.768 |      | kHz  |          |

# **@HITACHI**

Hitachi America Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

#### • ELECTRICAL CHARACTERISTICS - 2 (Ta =-40 to +85°C)

| Item                    | Symbol            | Test Conditions                                                                                                             | Val                    | ue   | Unit | Note |

|-------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------|------|------|------|

|                         | Symbol            | lest Conditions                                                                                                             | min                    | max  | Unit |      |

| Halt Duration Voltage   | V <sub>DH</sub>   | HLT = 0.2V                                                                                                                  | 2.3                    | _    | V    |      |

| Halt Current            | I <sub>DH</sub>   | V <sub>in</sub> = V <sub>CC</sub> , HLT = 0.2V,<br>V <sub>DH</sub> = 2.3V                                                   | -                      | 4.0  | μΑ   | (14) |

| Halt Delay Time         | t <sub>HD</sub>   |                                                                                                                             | 100                    | -    | μs   |      |

| Operation Recovery Time | t <sub>RC</sub>   |                                                                                                                             | 100                    | -    | μs   |      |

| HLT Fall Time           | t <sub>fHLT</sub> |                                                                                                                             | -                      | 1000 | μs   |      |

| HLT Rise Time           | trHLT             |                                                                                                                             | _                      | 1000 | μs   |      |

| HLT "Low" Hold Time     | tHLT              |                                                                                                                             | 400                    | _    | μs   |      |

| HLT "High" Hold Time    | tops              | R <sub>f</sub> Oscillation, External Clock Operation                                                                        | 100                    | -    | μs   |      |

| ···                     | J                 | Ceramic Filter Oscillation                                                                                                  | 4000                   | - '  | •    |      |

| Power Supply Rise Time  | trcc              | Built-in Reset, HLT = V <sub>CC</sub>                                                                                       | 0.1                    | 10   | ms   |      |

| Power Supply OFF Time   | toff              | Built-in Reset, HLT = V <sub>CC</sub>                                                                                       | 1                      | _    | ms   |      |

| RESET Pulse Width (1)   | <sup>†</sup> RST1 | External Reset, V <sub>CC</sub> = 4.5 to 5.5V, HLT = V <sub>CC</sub> (R <sub>f</sub> Oscillation, External Clock Operation) | 1                      |      | ms   |      |

|                         |                   | External Reset, V <sub>CC</sub> = 4.5 to 5.5V, HLT = V <sub>CC</sub> (Ceramic Filter Oscillation)                           | 4                      | -    |      |      |

| RESET Pulse Width (2)   |                   | External Reset, V <sub>CC</sub> = 4.5 to 5.5V, HLT = V <sub>CC</sub> , (Prescaler Clock = System Clock)                     | 2 • T <sub>inst</sub>  | _    |      |      |

| NESET Puise Width (2)   | t <sub>AST2</sub> | External Reset, V <sub>CC</sub> = 4.5 to 5.5V, HLT = V <sub>CC</sub> , (Prescaler Clock = Crystal Clock)                    | 32 x 10 <sup>6</sup> / | _    | μs   |      |

| RESET Rise Time         | t <sub>rAST</sub> | External Reset, HLT = V <sub>CC</sub> ,<br>V <sub>CC</sub> = 4.5 to 5.5V                                                    | _                      | 100  | μs   |      |

| RESET Fall Time         | t <sub>fRST</sub> | External Reset, $HLT = V_{CC}$ , $V_{CC} = 4.5$ to $5.5V$                                                                   | _                      | 100  | μs   |      |

(NOTE) 1. Applied to PMOS load of CMOS output pins and CMOS I/O common pins among D and R pins.

2. Applied to CMOS output pins, CMOS I/O common pins, input pins with pull up MOS, and I/O common pins with pull up MOS among D and R pins.

3. Applied to open-drain output pins and open-drain I/O common pins among D and R pins.

4. Pull up MOS current is excluded.

5. Applied to the supply current when the LCD-III is in the reset state and the crystal oscillation for timer doesn't operate. (Current that flows in the input/output circuit and in the power supply circuit for LCD is excluded).

Test Conditions: RESET, HLT, TEST = V<sub>CC</sub> (Reset State)

INTe, INT., INT., Roo to R 23, Do to D 3 = V<sub>CC</sub>

D<sub>14</sub>/X/O, D<sub>15</sub>/XI — D<sub>14</sub>/X/O, D<sub>15</sub>/XI = V<sub>CC</sub> (Crystal oscillation for timer is not selected).

V<sub>1</sub>, V<sub>3</sub>, V<sub>3</sub> = V<sub>CC</sub>

COM, to COM. SEG, to SEG, = Open

V<sub>1</sub>, V<sub>3</sub>, V<sub>3</sub> = V<sub>CC</sub>

COM<sub>1</sub> to COM<sub>4</sub>, SEG<sub>1</sub> to SEG<sub>32</sub> = Open

When the crystal oscillation for timer operates, the standby supply current (2) I<sub>CCS2</sub> flows in addition to I<sub>CC1</sub> or I<sub>CC2</sub>.

When the LCD-III is installed in the user's system, and in operation current increases according to the external circuitry and devices. Those are connected to the LCD-III. User should design the power supply in consideration of this point (The difference between the measured current in the above reset state and that measured in the operational state in the user's system is the increased part of the supply current).

6. Standby I/O leakage current is the leakage current of I/O pins in the "Halt" and "Disable" state.

7. Current that flows in the input/output circuit and in the power supply circuit for LCD is excluded. The standby supply current (2) is the supply current at V<sub>CC</sub> = 5½±10% in "Halt" state in the case that the crystal oscillation for timer is selected (only the crystal oscillator for timer, 5-bit divider and 6-bit prescaler are in operation).

- Power supply condition V<sub>CC</sub> ≥ V<sub>1</sub> ≥ V<sub>3</sub> ≥ V<sub>3</sub> ≥ GND should be maintained.

Applied to the following pins.

Input pins, I/O common pins with pull up MOS, and CMOS I/O common pins among D and R pins.

RESET, HLT, OSC<sub>3</sub>, INT<sub>8</sub> and INT<sub>3</sub>.

Applied to open-drain I/O common pins among D and R pins.

Current that flows in the input/output circuit and in the power supply circuit for LCD is excluded. The standby supply current is the supply current at V<sub>CC</sub> = 5V±10% in "Half" state in the case that the crystal oscillation for timer is not selected. The supply current when supply voltage falls to the Halt Duration Voltage is called "Halt Current" (I<sub>DH</sub>).

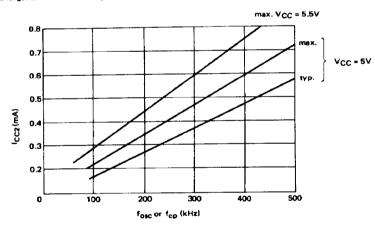

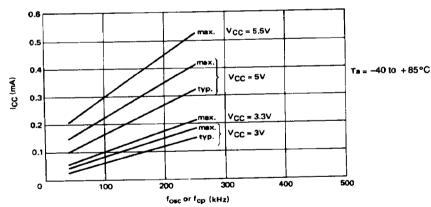

The supply current changes as follows according to operating frequency.

The voltage that drops between the power supply pins (V<sub>CC</sub>, V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub>) and each common or segment output pin.

The supply current at V<sub>CC</sub> = V<sub>DH</sub> = 2.3V in "Halt" state, in the case that the crystal oscillation for timer is not selected. Current that flows in the input/output circuit and in the power supply circuit for LCD is excluded.

## (1) HITACHI

Hitachi America Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300 190

This Material Copyrighted By Its Respective Manufacturer

15. Interrupt inputs must be retained for two or more cycles at both "High" and "Low" levels.

### ■ HD44795 ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 2.7 to 5.5V)

# ABSOLUTE MAXIMUM RATINGS

| Item                             | Symbol            | Value                        | Unit | Note                                                              |

|----------------------------------|-------------------|------------------------------|------|-------------------------------------------------------------------|

| Supply Voltage                   | Vcc               | -0.3 to +7.0                 | V    |                                                                   |

| Pin Voltage (1)                  | V <sub>T1</sub>   | -0.3 to V <sub>CC</sub> +0.3 | V    | Applied to all pins except those specified in V <sub>T2</sub> .   |

| Pin Voltage (2)                  | V <sub>T2</sub>   | 0.3 to +10.0                 | V    | Applied to open-drain output pins and open-drain I/O common pins. |

| Maximum Total Output Current (1) | -ΣI <sub>01</sub> | 45                           | mA   | (Note 3)                                                          |

| Maximum Total Output Current (2) | ΣΙ <sub>ο2</sub>  | 45                           | mA   | (Note 3)                                                          |

| Operating Temperature            | Topr              | -40 to +85°C                 | °C   |                                                                   |

| Storage Temperature              | T <sub>sto</sub>  | -55 to +125                  | °C   |                                                                   |

(NOTE) 1. Permanent LSI damage may occur if maximum ratings are exceeded.

Normal operation should be under the conditions of "ELECTRICAL CHARACTERISTICS-1, -2." If these conditions are exceeded, it could be cause of malfunction of LSI and affects reliability of LSI.

2. All voltages are with respect to GND.

3. Meximum Total Output Current is the total sum of output currents which can flow out or in simultaneously.

4. Power supply condition V<sub>CC</sub> ≥ V1 ≥ V2 ≥ V3 ≥ GND should be maintained.

# ● ELECTRICAL CHARACTERISTICS - 1 (V<sub>CC</sub> = 2.7 to 5.5V, T<sub>8</sub> =-40 to +85°C)

|                                       | Symbol Test Conditions |                                                                                                                                                                                   | min                                                                             |                           | Unit                             | Note     |          |                |

|---------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------|----------------------------------|----------|----------|----------------|

| item                                  | Symbol                 | 1031                                                                                                                                                                              | Total Containing                                                                |                           | typ                              | max      | v        |                |

| Input "Low" Voltage                   | VIL                    |                                                                                                                                                                                   |                                                                                 | -<br>V <sub>CC</sub> -0.4 |                                  | 0.4      |          | (0)            |

| Input "High" Voltage (1)              | V <sub>IH1</sub>       |                                                                                                                                                                                   | L .                                                                             |                           |                                  | Vcc      |          | (9)            |

| Input "High" Voltage (2)              | V <sub>IH2</sub>       |                                                                                                                                                                                   | V.                                                                              |                           |                                  | 10       | V        | (10)           |

| Output "Low" Voltage                  | VoL                    |                                                                                                                                                                                   | I <sub>OL</sub> = 0.4 mA                                                        |                           |                                  | 0.4      | ٧        |                |

| Output "High" Voltage (1)             | V <sub>OH1</sub>       | -I <sub>OH</sub> = 0.08 m                                                                                                                                                         | -I <sub>OH</sub> = 0.08 mA V <sub>4</sub>                                       |                           | _                                |          | <u> </u> | (1)            |

| Output "High" Voltage (2)             | V <sub>OH2</sub>       | -I <sub>OH</sub> = 0.01 m                                                                                                                                                         | -I <sub>OH</sub> = 0.01 mA V.                                                   |                           |                                  | -        | ٧        | (2)            |

| Driver Voltage Descending (COM)       | V <sub>d</sub> ,       | ld = 0.05 mA                                                                                                                                                                      |                                                                                 | -                         | _                                | 0.4      | ٧        | (13)           |

| Driver Voltage Descending (SEG)       | V <sub>d</sub> ,       | Id = 0.01 mA                                                                                                                                                                      |                                                                                 | -                         | _                                | 0.4      | V        | (13)           |

| Dividing Resistor of LCD Power Supply | Rwell                  |                                                                                                                                                                                   |                                                                                 | 25                        | _                                | 300      | kΩ       |                |

| Interrupt Input Hold Time             | tint                   |                                                                                                                                                                                   |                                                                                 | 2·T <sub>inst</sub>       | -                                |          | μs       | (15)           |

| Interrupt Input Fall Time             | tfINT                  |                                                                                                                                                                                   |                                                                                 |                           | <u> </u>                         | 50<br>50 | μs       | (15)           |

| Interrupt Input Rise Time             | trINT                  |                                                                                                                                                                                   |                                                                                 |                           | <del>-</del> -                   |          |          | (3)            |

| Output "High" Current                 | Юн                     | V <sub>OH</sub> = 10V                                                                                                                                                             |                                                                                 |                           |                                  | 3        | μΑ       |                |

| In the Comment                        | ایر                    | $V_{in} = 0$ to $V_{c}$                                                                                                                                                           |                                                                                 | <u> </u>                  |                                  | 1.0      | μΑ       | (3), (         |

| Input Leakage Current                 | '11                    | V <sub>in</sub> = 0 to 10                                                                                                                                                         | V                                                                               | <del></del> _             |                                  | 3        |          | (3), (1        |

| Pull up MOS Current                   | -IP                    | V <sub>CC</sub> = 3V                                                                                                                                                              |                                                                                 | 15                        |                                  | 80       | μΑ       | <u> </u>       |

| Supply Current                        | Icc                    | V <sub>in</sub> = V <sub>CC</sub> , V <sub>CC</sub> = 3V<br>R <sub>f</sub> Oscillation<br>(f <sub>osc</sub> = 200 kHz)<br>External Clock Operation<br>(f <sub>cp</sub> = 200 kHz) |                                                                                 | -                         | _                                | 0.15     | mA       | (5),(          |

|                                       | T                      | HLT                                                                                                                                                                               | Vin = 0 to Vcc                                                                  |                           |                                  | 1.0      | μΑ       | (6),(          |

| Standby I/O Leakage Current           | ILS                    | = 0.5V                                                                                                                                                                            | V <sub>in</sub> = 0 to 10V                                                      |                           | L -                              | 3        | μΑ       | (6), (         |

| Standby Supply Current (1)            | I <sub>CCS1</sub>      | V <sub>CC</sub> = 2.7 to                                                                                                                                                          | V <sub>in</sub> = V <sub>CC</sub> , HLT = 0.1V<br>V <sub>CC</sub> = 2.7 to 3.3V |                           |                                  | 6        | μА       | (11            |

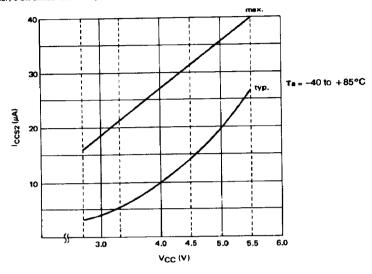

| Standby Supply Current (2)            | I <sub>CCS2</sub>      | V <sub>in</sub> = V <sub>CC</sub> , HLT = 0.1V<br>V <sub>CC</sub> = 2.7 to 3.3V                                                                                                   |                                                                                 | -                         |                                  | 21       | μΑ       | (7)            |

| Frame Frequency of LCD Drive          | f <sub>F</sub>         | n = 2 (1/2 Do<br>n = 3 (1/3 Do                                                                                                                                                    | n = 1 (static)<br>n = 2 (1/2 Duty)<br>n = 3 (1/3 Duty)<br>n = 4 (1/4 Duty)      |                           | 1<br>128 x n x T <sub>inst</sub> |          |          |                |

| LCD Display Voltage                   | VLCD                   | V <sub>CC</sub> -V <sub>3</sub>                                                                                                                                                   |                                                                                 | 2.5                       | <u> </u>                         | Vcc      |          | (8)            |

| External Clock Operation, System      | Clock                  |                                                                                                                                                                                   |                                                                                 |                           |                                  | r        | ·        | - <del>-</del> |

| External Clock Frequency              | f <sub>cp</sub>        |                                                                                                                                                                                   |                                                                                 | 40                        | 200                              | 240      | kHz      |                |

| External Clock Duty                   | Duty                   |                                                                                                                                                                                   |                                                                                 | 45                        | 50                               | 55       | %        | 1              |

| External Clock Rise Time              | t <sub>rop</sub>       |                                                                                                                                                                                   |                                                                                 | 0                         | <u> </u>                         | 0.2      | μs       | $\perp$        |

| External Clock Fall Time              | t <sub>fop</sub>       |                                                                                                                                                                                   |                                                                                 | 0                         |                                  | 0.2      | μs       |                |

| Instruction Cycle Time                | Tinst                  | T <sub>inst</sub> = 4/f <sub>cp</sub>                                                                                                                                             |                                                                                 | 16.6                      | 20                               | 100      | μs       |                |

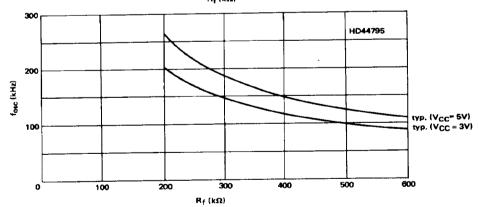

| Internal Clock Operation (Rf Osc      |                        |                                                                                                                                                                                   |                                                                                 |                           |                                  |          | <b>.</b> | <b>~</b> ~ ~ . |

| Clock Oscillation Frequency           | fosc                   | R <sub>f</sub> =                                                                                                                                                                  | V <sub>CC</sub> = 2.7 to 3.3V                                                   | 150                       |                                  | 250      | kHz      |                |

|                                       |                        | 200kΩ±2%                                                                                                                                                                          | V <sub>CC</sub> = 2.7 to 5.5V                                                   | 150                       |                                  | 350      | Kriz     |                |

|                                       | +                      | Tinst =                                                                                                                                                                           | V <sub>CC</sub> = 2.7 to 3.3V                                                   |                           | T-                               | 26.6     | μs       |                |

| Instruction Cycle Time                | Tinst                  | 4/fosc                                                                                                                                                                            | V <sub>CC</sub> = 2.7 to 5.5V                                                   | 11.4                      | -                                | 26.6     | μ        | Ш.             |

| Internal Clock Operation (Crystal     | Oscillation            |                                                                                                                                                                                   |                                                                                 |                           |                                  |          |          |                |

| Clock Oscillation Frequency           | foscx                  | Crystal                                                                                                                                                                           |                                                                                 | -1 <b></b>                | 32.768                           |          | kHz      | ٦              |

# (1) HITACHI

192

### • ELECTRICAL CHARACTERISTICS -2 (Ta =-40 to +85°C)

| Item                                    | Symbol            | Test Conditions                                                                                                  | Val                                         | ue   | Unit | Note |

|-----------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------|------|------|

|                                         |                   | Test Conditions                                                                                                  | min                                         | max  | J 0  |      |

| Halt Duration Voltage                   | V <sub>DH</sub>   | HLT = 0.2 V                                                                                                      | 2.3                                         | _    | V    |      |

| Halt Current                            | Грн               | V <sub>in</sub> = V <sub>CC</sub> , HLT = 0.1V,<br>V <sub>DH</sub> = 2.3V                                        | _                                           | 4.0  | μΑ   | (14) |

| Halt Delay Time                         | t <sub>HD</sub>   |                                                                                                                  | 100                                         | _    | μς   |      |

| Operation Recovery Time                 | tRC               |                                                                                                                  | 100                                         | _    | μs   |      |

| HLT Fall Time                           | t <sub>fHLT</sub> |                                                                                                                  |                                             | 1000 | μs   | 1    |

| HLT Rise Time                           | t <sub>rHLT</sub> |                                                                                                                  |                                             | 1000 | μs   |      |

| HLT "Low" Hold Time                     | t <sub>HLT</sub>  |                                                                                                                  | 400                                         | _    | μs   |      |

| HLT "High" Hold Time                    | tops              | R <sub>f</sub> Oscillation, External Clock Operation                                                             | 100                                         | -    | μs   |      |

| Power Supply Rise Time                  | trcc              | Built-in Reset, HLT = V <sub>CC</sub>                                                                            | 0.1                                         | 10   | ms   |      |

| Power Supply OFF Time                   | toff              | Built-in Reset, HLT = V <sub>CC</sub>                                                                            | 1                                           | _    | ms   | 1    |

| RESET Pulse Width (1)                   | t <sub>RST1</sub> | External Reset, HLT = V <sub>CC</sub>                                                                            | 1                                           | _    | ms   |      |

|                                         |                   | External Reset, V <sub>CC</sub> = 2.7<br>to 5.5V, HLT = V <sub>CC</sub> ,<br>(Prescaler Clock = System<br>Clock) | 2.T <sub>inst</sub>                         | _    |      |      |

| RESET Pulse Width (2) t <sub>RST2</sub> | t <sub>RST2</sub> | External Reset, V <sub>CC</sub> = 2.7 to 5.5V, HLT = V <sub>CC</sub> , (Prescaler Clock = Crystal Clock)         | 32 x 10 <sup>6</sup> /<br>f <sub>oscx</sub> |      | μs   |      |

| RESET Rise Time                         | trest             | External Reset, HLT = V <sub>CC</sub> ,<br>V <sub>CC</sub> = 2.7 to 5.5V                                         | -                                           | 100  | μs   |      |

| RESET Fall Time                         | trest             | External Reset, HLT = V <sub>CC</sub> ,<br>V <sub>CC</sub> = 2.7 to 5.5V                                         | _                                           | 100  | μs   |      |

(NOTE)

1. Applied to PMOS load of CMOS output pins and CMOS I/O common pins among D and R pins.

2. Applied to CMOS output pins, CMOS I/O common pins, input pins with pull up MOS, and I/O common pins with pull up MOS among D and R pins.

3. Applied to open-drein output pins and open-drein I/O common pins among D and R pins.

4. Pull up MOS current is excluded.

5. Applied to the supply current when the LCD-I/II is in the reset state and the crystal oscillation for timer doesn't operate (Current that flows in the input/output circuit and in the power supply circuit for LCD is excluded).

Test Conditions: RESET, HLT, TEST = V<sub>CC</sub> (Reset State)

INTe, INTI, Ro, to Ros., O, to D<sub>12</sub> + V<sub>CC</sub>

D<sub>14</sub>/XO, D<sub>15</sub>/XI — D<sub>16</sub>/XO = Open, D<sub>15</sub>/XI = V<sub>CC</sub> (Crystal oscillation for timer is not selected).

When the crystal oscillation for timer is selected).

V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub> = V<sub>CC</sub>

COM<sub>1</sub> to COM<sub>2</sub>, SEG<sub>1</sub> to SEG<sub>32</sub> = Open

When the crystal oscillation for timer operates, the standby supply current (2) I<sub>CCS2</sub> flows in addition to I<sub>CC</sub>.

When the LCD-III is installed in the user's system, and in operation current increases according to the external circuitry and devices. Those are connected to the LCD-III. User should design the power supply in consideration of this point (The difference between the measured current in the above reset state and that measured in the operational state in the user's system is the increased part of the supply current).

8. Standby I/O leakage current is the leakage current of I/O pins in the "Helt" and "Disable" state.

7. Current that flows in the input/output circuit and in the power supply circuit for LCD is excluded. The standby supply current (2) is the supply current at V<sub>CC</sub> = 3V±10% in "Halt" state in the case that the crystal oscillation for timer is selected (only the crystal oscillator for timer, 5-bit divider and 6-bit prescaler are in operation).

- Power supply condition V<sub>CC</sub> ≥ V<sub>1</sub> ≥ V<sub>2</sub> ≥ V<sub>3</sub> ≥ GND should be maintained.

Applied to the following pins.

Input pins, I/O common pins with pull up MOS, and CMOS I/O common pins among D and R pins.

RESET, HLT, OSC1, INTs and INTs.

Applied to open-drain I/O common pins among D and R pins.

Current that flows in the input/output circuit and in the power supply circuit for LCD is excluded. The standby supply current is the supply current at V<sub>CC</sub> = 3V±10% in "Half" state in the case that the crystal oscillation for timer is not selected. The supply current set V<sub>CC</sub> = 3V±10% in "Half" state in the case that the crystal oscillation for timer is not selected. The supply current set V<sub>CC</sub> = 3V±10% in "Half" state in the case that the crystal oscillation for timer is not selected. The supply current changes as follows according to operating frequency.

# (C) HITACHI

Hitachi America Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300 194

This Material Copyrighted By Its Respective Manufacturer

- The voltage that drops between the power supply pins (V<sub>CC</sub>, V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub>) and each common or segment output pin.

The supply current at V<sub>CC</sub> = V<sub>DM</sub> = 2.3V in "Helt" state, in the case that the crystal oscillation for timer is not selected. Current that flows in the input/output circuit and in the power supply circuit for LCD is excluded.

Interrupt inputs must be retained for two or more cycles at both "High" and "Low" levels.

#### - SIGNAL DESCRIPTION

The input and output signals for the LCD-III shown in PIN ARRANGEMENT are described in the following paragraphs.

### VCC and GND

Power is supplied to the LCD-III using these two pins. VCC is power and GND is the ground connection.

#### • RESET

This pin resets the LCD-III independently of the automatic resetting capability (ACL; Built-in Reset Circuit) already in the LCD-III. The LCD-III can be reset by pulling RESET High.

Refer to RESET FUNCTION for additional information.

### OSC<sub>1</sub> and OSC<sub>2</sub>

These pins provide control input for the on-chip clock oscillator circuit. A resistor, a ceramic filter circuit, or an external oscillator can be connected to these pins to provide a system clock with various degrees of stability/cost tradeoffs. Lead length and stray capacitance on these two pins should be minimized.

Refer to OSCILLATOR for recommendations about these pins.

This pin is used to enter the LCD-III into the HALT state (Stand-by Mode). The LCD-III can be moved into the halt state by pulling HLT Low.

In the halt state the internal clock stops and all the internal statuses (RAM, Registers, Carry, Status, Program Counter, etc.) are maintained. Consequently power consumption is greatly reduced. By pulling HLT high, the LCD-III starts operation from the status just before the halt state.

Refer to HALT FUNCTION for details of halt mode.

This pin is not for user application and must be connected to VCC.

These pins generate interrupt request to the LCD-III. Refer to INTERRUPT for additional information.

#### V<sub>1</sub>, V<sub>2</sub> and V<sub>3</sub>

Power for liquid crystal display are supplied to the LCD-III using these pins ( $V_{CC} \ge V_1 \ge V_2 \ge V_3 \ge GND$ ).

#### Rm to Rm

These four lines are a 4-bit input channel.

Refer to INPUT/OUTPUT for additional information.

#### R<sub>10</sub> to R<sub>13</sub>, R<sub>20</sub> to R<sub>23</sub>

These 8 lines are arranged into two 4-bit Input/Output common channels. 4-bit registers (data I/O register) are attached to these channels. Each channel is directly addressed by the operand of an instruction. I/O configuration of each pin can be specified among Open Drain, With Pull Up MOS, and CMOS

using a mask option.

Refer to INPUT/OUTPUT for additional information.

#### R<sub>30</sub> to R<sub>33</sub>

These four lines are a 4-bit output channel. 4-bit register is attached to this channel. This channel is directly addressed by the operand of an instruction. I/O configuration of each pin can be specified among Open Drain and CMOS using a mask option.

Refer to INPUT/OUTPUT for additional information.

#### Do to D13

These are 14 discrete signals which can be configured as Input/Output lines.

Refer to INPUT/OUTPUT for additional information.

### D14/XO, D15/XI

$D_{14}/XO$  and  $D_{15}/XI$  select in the following 3 types with a mask option.

- Discrete I/O (common pin)

- Crystal circuit connecting pins (with internal halt)

- Crystal circuit connecting pins (no internal halt)

# Refer to INPUT/OUTPUT for additional information.

#### ● COM₁ to COM4

These pins are common pins for liquid crystal display. Refer to LIQUID CRYSTAL DISPLAY for additional information.

# • SEG<sub>1</sub> to SEG<sub>32</sub>

These are segment pins for liquid crystal display.

# ((D) HITACHI

Refer to LIQUID CRYSTAL DISPLAY for additional information.

#### ■ OSCILLATOR

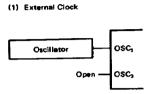

A resistor, a ceramic filter circuit or an external oscillator can be connected to  $OSC_1$  and  $OSC_2$ . However, a ceramic filter circuit cannot be used on the HD44795. The connection methods are shown in Figure 1.

Length of the wirings for OSC<sub>1</sub> and OSC<sub>2</sub> pins should be minimized because the oscillation frequency varies depending on the capacitance of these pins.

Figure 1 Connection Methods for Oscillator (to be continued)

# (1) HITACHI

196 Hitachi America Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

This Material Copyrighted By Its Respective Manufacturer