# HPC46083MH High-Performance microController Emulator

#### **General Description**

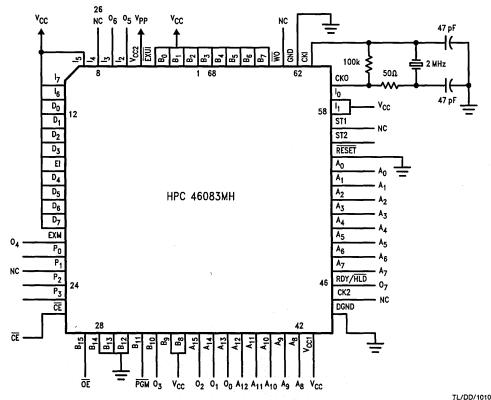

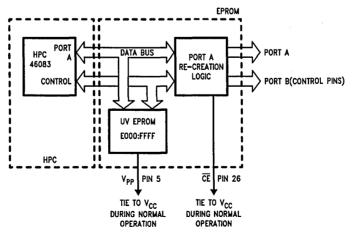

The HPC46083MH is the emulator device for the HPC16083 and is a member of the HPCTM family of High Performance microControllers. Each member of the family has the same core CPU with a unique memory and I/O configuration to suit specific applications. The HPC46083MH has 8k bytes of on-chip EPROM. The HPC46083MH is a two chip system packaged in a dual cavity ceramic LDCC type package, with a lid on top, and a UV quartz window on bottom. Within the package is an HPC46083 and UV-erasable EPROM with port recreation logic. The EPROM die allows the HPC to function normally, while executing code out of the EPROM. The HPC46083MH may be programmed using a programming card to adapt the part to a normal 27C64 EPROM programmer. The part will function as the normal HPC, and the use of the EPROM should be transparent to the user. The only system design consideration is that pin 5 is VPP, not VCC, and should be tied to VCC during normal operation. Pin 26 should also be tied to VCC.

The HPC devices are complete microcomputers on a single chip. All system timing, internal logic, RAM, and I/O are provided on the chip to produce a cost effective solution for high performance applications. On-chip functions such as UART, up to eight 16-bit timers with 4 input capture registers, vectored interrupts, WATCHDOGTM logic and MICRO-WIRE/PLUSTM provide a high level of system integration. The ability to address up to 64k bytes of external memory enables the HPC to be used in powerful applications typically performed by microprocessors and expensive peripheral chips.

The HPC46083MH is available in 68-pin LDCC type packages.

#### **Features**

- HPC family—core features:

- 16-bit architecture, both byte and word

- 16-bit data bus, ALU, and registers

- 64k bytes of external memory addressing

- FAST—200 ns for fastest instruction when using 20.0 MHz clock

- High code efficiency—most instructions are single byte

- 16 x 16 multiply and 32 x 16 divide

- Eight vectored interrupt sources

- Four 16-bit timer/counters with 4 synchronous outputs and WATCHDOG logic

- MICROWIRE/PLUS serial I/O interface

- CMOS—very low power with two power save modes: IDLE and HALT

- UART—full duplex, programmable baud rate

- Four additional 16-bit timer/counters with pulse width modulated outputs

- Four input capture registers

- 52 general purpose I/O lines (memory mapped)

- 8k bytes of EPROM, 256 bytes of RAM on chip

- Commercial (0°C to +70°C)

## Block Diagram (HPC46083 with 8k EPROM shown)

#### 20 MHz Absolute Maximum Ratings

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Total Allowable Source or Sink Current

Storage Temperature Range

-65°C to +150°C

Lead Temperature (Soldering, 10 sec)

300°C

$V_{CC}$  with Respect to GND -0.5V to 7.0V All Other Pins  $(V_{CC}+0.5)V$  to (GND-0.5)V ESD 2000V

Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

#### DC Electrical Characteristics $V_{CC} = 5.0V \pm 10\%$ unless otherwise specified, $T_A = 0^{\circ}C$ to $+70^{\circ}C$

| Symbol           | Parameter                                                                                                     | Test Conditions                                             | Min                   | Max                 | Units |

|------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------|---------------------|-------|

| ICC <sub>1</sub> | Supply Current                                                                                                | V <sub>CC</sub> = 5.5V, f <sub>in</sub> = 20.0 MHz (Note 1) |                       | 134                 | mA    |

| •                | 54 + 4 × f <sub>in</sub>                                                                                      | V <sub>CC</sub> = 5.5V, f <sub>in</sub> = 2.0 MHz (Note 1)  |                       | 62                  | mA    |

| I <sub>CC2</sub> | IDLE Mode Current                                                                                             | $V_{CC} = 5.5V$ , $f_{in} = 20.0$ MHz, (Note 1)             |                       | 26                  | mA    |

| -                | 0.5 + 1.25 × f <sub>in</sub>                                                                                  | V <sub>CC</sub> = 5.5V, f <sub>in</sub> = 2.0 MHz, (Note 1) |                       | 3                   | mA    |

| I <sub>CC3</sub> | HALT Mode Current                                                                                             | V <sub>CC</sub> = 5.5V, f <sub>in</sub> = 0 kHz, (Note 1)   |                       | 2                   | mA    |

| ·                |                                                                                                               | V <sub>CC</sub> = 2.5V, f <sub>in</sub> = 0 kHz, (Note 1)   |                       | 250                 | μΑ    |

| INPUT VO         | LTAGE LEVELS RESET, NMI, CKI A                                                                                | ND WO (SCHMITT TRIGGERED)                                   |                       |                     |       |

| V <sub>IH1</sub> | Logic High                                                                                                    |                                                             | 0.9 V <sub>CC</sub>   |                     | ٧     |

| V <sub>IL1</sub> | Logic Low                                                                                                     | ·                                                           |                       | 0.1 V <sub>CC</sub> | ٧     |

| ALL OTH          | ER INPUTS                                                                                                     |                                                             |                       |                     |       |

| V <sub>IH2</sub> | Logic High                                                                                                    |                                                             | 0.7 V <sub>CC</sub>   |                     | v     |

| V <sub>IL2</sub> | Logic Low                                                                                                     |                                                             |                       | 0.2 V <sub>CC</sub> | V     |

| l <sub>Ll</sub>  | Input Leakage Current                                                                                         |                                                             |                       | ±1                  | μΑ    |

| Cı               | Input Capacitance                                                                                             | (Note 2)                                                    |                       | 10                  | pF    |

| C <sub>IO</sub>  | I/O Capacitance                                                                                               | (Note 2)                                                    |                       | 20                  | pF    |

| OUTPUT           | VOLTAGE LEVELS                                                                                                |                                                             |                       |                     |       |

| V <sub>OH1</sub> | Logic High (CMOS)                                                                                             | $I_{OH} = -10 \mu\text{A} (\text{Note 2})$                  | V <sub>CC</sub> - 0.1 |                     | V     |

| V <sub>OL1</sub> | Logic Low (CMOS)                                                                                              | I <sub>OH</sub> = 10 μA (Note 2)                            |                       | 0.1                 | ٧     |

| V <sub>OH2</sub> | Port A/B Drive, CK2                                                                                           | I <sub>OH</sub> = -7 mA                                     | 2.4                   |                     | V     |

| V <sub>OL2</sub> | (A <sub>0</sub> -A <sub>15</sub> , B <sub>10</sub> , B <sub>11</sub> , B <sub>12</sub> , B <sub>15</sub> )    | I <sub>OL</sub> = 3 mA                                      |                       | 0.4                 | V     |

| V <sub>OH3</sub> | Other Port Pin Drive, WO (open                                                                                | I <sub>OH</sub> = -1.6 mA                                   | 2.4                   |                     | V     |

| V <sub>OL3</sub> | drain) (B <sub>0</sub> -B <sub>9</sub> , B <sub>13</sub> , B <sub>14</sub> , P <sub>0</sub> -P <sub>3</sub> ) | I <sub>OL</sub> = 0.5 mA                                    |                       | 0.4                 | V     |

| V <sub>OH4</sub> | ST1 and ST2 Drive                                                                                             | I <sub>OH</sub> = -6 mA                                     | 2.4                   |                     | ٧     |

| V <sub>OL4</sub> |                                                                                                               | I <sub>OL</sub> = 1.6 mA                                    |                       | 0.4                 | V     |

| VRAM             | RAM Keep-Alive Voltage                                                                                        | (Note 3)                                                    | 2.5                   | Vcc                 | v     |

| loz              | TRI-STATE Leakage Current                                                                                     |                                                             |                       | ±5                  | μА    |

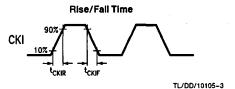

Note 1:  $I_{CC_1}$ ,  $I_{CC_2}$ ,  $I_{CC_3}$  measured with no external drive ( $I_{OH}$  and  $I_{OL} = 0$ ,  $I_{IH}$  and  $I_{IL} = 0$ ).  $I_{CC_1}$  is measured with  $\overline{\text{RESET}} = V_{SS}$ .  $I_{CC_3}$  is measured with NMI =  $V_{CC}$ . CKI driven to  $V_{IH1}$  and  $V_{IL1}$ , with rise and fall times less than 10 ns.

Note 2: This is guaranteed by design and not tested.

Note 3: Test duration is 100 ms.

# 20 MHz (1 Wait State Operation) AC Electrical Characteristics $V_{CC}=5.0V\pm10\%$ unless otherwise specified, $T_A=0^{\circ}C$ to $+70^{\circ}C$

| Symbol                                                               | Parameter                                          | Min | Max  | Units |

|----------------------------------------------------------------------|----------------------------------------------------|-----|------|-------|

| $f_C = CKI freq.$                                                    | Operating Frequency (Note 4)                       | 2   | 20.0 | MHz   |

| $t_{C1} = 1/f_{C}$                                                   | Clock Period                                       | 50  | 500  | ns    |

| t <sub>CKIR</sub> (Note 3)                                           | CKI Rise Time                                      |     | 7    | ns    |

| t <sub>CKIF</sub> (Note 3)                                           | CKI Fall Tiime                                     |     | 7    | ns    |

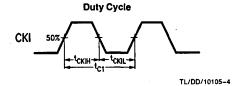

| [t <sub>CKIH</sub> /<br>(t <sub>CKIH</sub> + t <sub>CKIL</sub> )]100 | Duty Cycle                                         | 45  | 55   | %     |

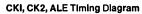

| $t_{\rm C} = 2/f_{\rm C}$                                            | Timing Cycle                                       | 100 | 1000 | ns    |

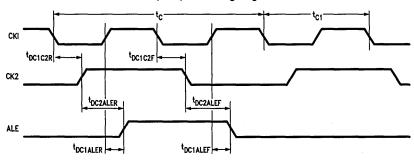

| $t_{LL} = \frac{1}{2} t_{C} - 12$                                    | ALE Pulse Width                                    | 38  |      | ns    |

| t <sub>DC1C2R</sub><br>(Notes 1, 2)                                  | Delay from CKI Falling<br>Edge to CK2 Rising Edge  | 0   | 55   | ns    |

| t <sub>DC1C2F</sub><br>(Notes 1, 2)                                  | Delay from CKI Falling<br>Edge to CK2 Falling Edge | 0   | 55   | ns    |

| t <sub>DC1ALER</sub> (Notes 1, 2)                                    | Delay from CKI Rising<br>Edge to ALE Rising Edge   | 10  | 50   | ns    |

| t <sub>DC1ALEF</sub> (Notes 1, 2)                                    | Delay from CKI Rising<br>Edge to ALE Falling Edge  | 10  | 50   | ns    |

| t <sub>DC2ALER = 1/4 tC</sub> + 35<br>(Note 2)                       | Delay from CK2 Rising<br>Edge to ALE Rising Edge   |     | 65   | ns    |

| t <sub>DC2ALEF</sub> = 1/4 tC + 35<br>(Note 2)                       | Delay from CK2 Falling<br>Edge to ALE Falling Edge |     | 65   | ns    |

| $t_{ST} = \frac{1}{4}t_{C} - 20$                                     | Address Valid to ALE Falling Edge                  | 5   |      | ns    |

| $t_{VP} = \frac{1}{4}t_C - 5 \qquad .$                               | Address Hold from ALE Falling Edge                 | 20  |      | ns    |

| $t_{WAIT} = t_C = WS$                                                | Wait State Period                                  | 100 |      | ns    |

| $f_{XIN} = f_C/19$                                                   | External Timer Input Frequency                     |     | 1.05 | MHz   |

| t <sub>XIN</sub>                                                     | Pulse Width for Timer Inputs                       | 100 |      | ns    |

| f <sub>MW</sub>                                                      | External MICROWIRE/PLUS Clock Input Frequency      |     | 1.25 | MHz   |

| $f_U = f_C/8$                                                        | External UART Clock Input Frequency                |     | 2.5  | MHz   |

# **CKI Input Signal Characteristics**

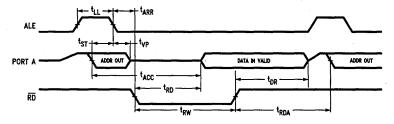

## **Read Cycle Timing**

| Symbol                                | Parameter                           | Min | Max | Units |

|---------------------------------------|-------------------------------------|-----|-----|-------|

| $t_{ARR} = \frac{1}{4}t_{C} - 5$      | ALE Falling Edge to RD Falling Edge | 20  |     | ns    |

| $t_{RW} = \frac{1}{2}t_{C} + WS - 10$ | RD Pulse Width                      | 140 |     | ns    |

| $t_{DR} = \frac{3}{4}t_{C} - 20$      | Data Hold after Rising Edge of RD   | .0  | 55  | ns    |

| $t_{ACC} = t_C + WS - 85$ (Note 2)    | Address Valid to Input Data Valid   |     | 115 | ns    |

| $t_{RD} = \frac{1}{2}t_{C} + WS - 85$ | RD Falling Edge to Input Data Valid |     | 65  | ns    |

| $t_{RDA} = t_{C} - 5$                 | RD Rising Edge to Address Valid     | 95  |     | ns    |

Note: Bus Output (Port A)  $C_L = 100$  pF, CK2 Output  $C_L = 50$  pF, other Outputs  $C_L = 80$  pF. AC parameters are tested using DC Characteristics Inputs and non CMOS Outputs. Measurement of AC specifications is done with external clock driving CKI with 50% duty cycle. The capacitive load on CKO must be kept below 15 pF or AC measurements will be skewed.

Note: WS = t<sub>WAIT</sub> \* number of pre-programmed wait states. Minimum and Maximum values are calculated from maximum operating frequency with one (1) wait state pre-programmed.

Note 1: Do not design with this parameter unless CKI is driven with an active signal. When using a passive crystal circuit, CKI or CKO should not be connected to any external logic since any load (besides the passive components in the crystal circuit) will affect the stability of the crystal unpredictably.

Note 2: These are not directly tested parameters. Therefore the given min/max value cannot be guaranteed. It is, however, derived from measured parameters, and may be used for system design with a high confidence level.

Note 3: This is guaranteed by design and not tested.

Note 4: Maximum frequency with 0 wait states is 6 MHz.

## **Write Cycle Timing**

| Symbol                                | Parameter                              | Min | Max | Units |

|---------------------------------------|----------------------------------------|-----|-----|-------|

| $t_{ARW} = \frac{1}{2}t_{C} - 5$      | ALE Falling Edge to WR Falling Edge    | 45  |     | ns    |

| $t_{WW} = \frac{3}{4}t_{c} + WS - 20$ | WR Pulse Width                         | 155 |     | ns    |

| $t_{HW} = \frac{1}{4}t_C - 5$         | Data Hold after<br>Rising Edge of WR   | 20  |     | ns    |

| $t_V = \frac{1}{2}t_C + WS - 20$      | Data Valid before<br>Rising Edge of WR | 130 |     | ns    |

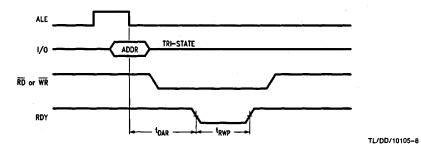

## **Ready/Hold Timing**

| Symbol                                       | Parameter                                      | Min | Max  | Units |

|----------------------------------------------|------------------------------------------------|-----|------|-------|

| $t_{DAR} = \frac{1}{4}t_{C} + WS - 80$       | Falling Edge of ALE<br>to Falling Edge of RDY  |     | 45   | ns    |

| $t_{RWP} = t_C + 10$                         | RDY Pulse Width                                | 110 |      | ns    |

| t <sub>SALE</sub> = 11/4 t <sub>C</sub> + 70 | Falling Edge of HLD<br>to Rising Edge of ALE   | 145 |      | ns    |

| $t_{HWP} = t_C + 10$                         | HLD Pulse Width                                | 110 |      | ns    |

| $t_{HAD} = \frac{11}{4}t_{C} + 70$           | Rising Edge on HLD to<br>Rising Edge on HLDA   |     | 345  | ns    |

| $t_{HAE} = 2t_{C} + 130$                     | Falling Edge on HLD to<br>Falling Edge on HLDA |     | 330* | ns    |

| $t_{BF} = \frac{1}{2}t_{C} + 66$             | Bus Float after<br>Falling Edge on HLDA        |     | 116  | ns    |

| $t_{BE} = \frac{1}{2} t_{C} + 66$            | Bus Enable before<br>Rising Edge of HLDA       | 116 |      | ns    |

<sup>\*</sup>Note: tHAE may be as long as (6t<sub>C</sub> + 8ws + 144t<sub>C</sub> + 180) depending on which instruction is being executed, the addressing mode and number of wait states. that maximum value tested is for the optimal case.

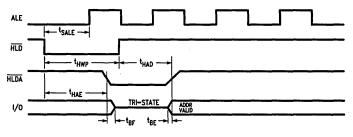

|                   | Parameter                                     | Min | Max | Units |

|-------------------|-----------------------------------------------|-----|-----|-------|

| tuas              | Address Setup Time to<br>Falling Edge of URD  | 10  |     | ns    |

| t <sub>UAH</sub>  | Address Hold Time from<br>Rising Edge of URD  | 10  |     | ns    |

| t <sub>RPW</sub>  | URD Pulse Width                               | 100 |     | ns    |

| t <sub>OE</sub>   | URD Falling Edge to Output Data Valid         | 0   | 60  | ns    |

| top               | Rising Edge of URD to Output Data Invalid     | 5   | 70  | ns    |

| t <sub>DRDY</sub> | RDRDY Delay from Rising Edge of URD           |     | 70  | ns    |

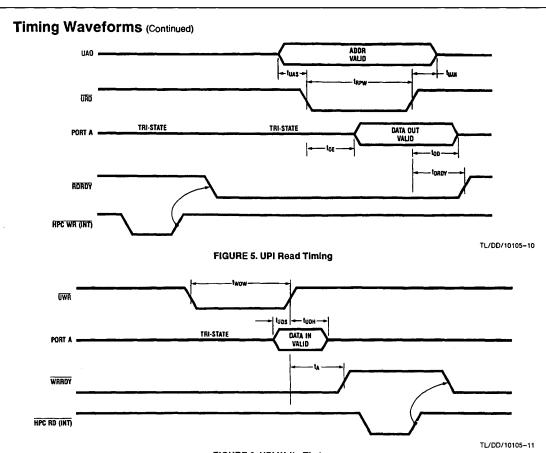

| twow              | UWR Pulse Width                               | 40  |     | ns    |

| t <sub>UDS</sub>  | Input Data Valid before<br>Rising Edge of UWR | 10  |     | ns    |

| t <sub>UDH</sub>  | Input Data Hold after<br>Rising Edge of UWR   | 20  |     | ns    |

t<sub>A</sub>

WRRDY

Delay from Rising

Edge of UWR

Note: Bus Output (Port A) C<sub>L</sub> = 100 pF, CK2 Output C<sub>L</sub> = 50 F, other Outputs C<sub>L</sub> = 80 pF.

# **Timing Waveforms**

TL/DD/10105-5

70

# Timing Waveforms (Continued)

FIGURE 1. Write Cycle

TL/DD/10105-6

TL/DD/10105-7

FIGURE 2. Read Cycle

FIGURE 3. Ready Mode Timing

FIGURE 4. Hold Mode Timing

#### FIGURE 6. UPI Write Timing

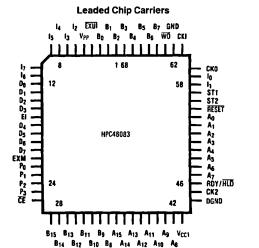

#### **Pin Descriptions**

The HPC46083MH is available in 68-pin LDCC packages.

#### I/O PORTS

Port A is a 16-bit bidirectional I/O port with a data direction register to enable each separate pin to be individually defined as an input or output. When accessing external memory, port A is used as the multiplexed address/data bus.

Port B is a 16-bit port with 12 bits of bidirectional I/O similar in structure to Port A. Pins B10, B11, B12 and B15 are general purpose outputs only in this mode. Port B may also be configured via a 16-bit function register BFUN to individually allow each pin to have an alternate function.

| allow | each pin | to nave an alternate function.         |

|-------|----------|----------------------------------------|

| B0:   | TDX      | UART Data Output                       |

| B1:   |          |                                        |

| B2:   | CKX      | UART Clock (Input or Output)           |

| B3:   | T2IO     | Timer2 I/O Pin                         |

| B4:   | T310     | Timer3 I/O Pin                         |

| B5:   | SO       | MICROWIRE/PLUS Output                  |

| B6:   | SK       | MICROWIRE/PLUS Clock (Input or Output) |

| B7:   | HLDA     | Hold Acknowledge Output                |

| B8:   | TS0      | Timer Synchronous Output               |

| B9:   | TS1      | Timer Synchronous Output               |

| B10:  | UA0      | Address 0 Input for UPI Mode           |

| B11:  | WRRDY    | Write Ready Output for UPI Mode        |

| B12:  |          |                                        |

| B13: | TS2                         | Timer Synchronous Output                |

|------|-----------------------------|-----------------------------------------|

| B14: | TS3                         | Timer Synchronous Output                |

| B15: | RDRDY                       | Read Ready Output for UPI Mode          |

|      |                             | cternal memory, four bits of port B are |

|      | accessing ex<br>is follows: | cternal memory, four bits of port B     |

| B10: | ALE | Address Latch Enable Output   |

|------|-----|-------------------------------|

| B11: | WR  | Write Output                  |

| B12: | HBE | High Byte Enable Output/Input |

|      |     | (sampled at reset)            |

| R15. | BD  | Read Output                   |

Port I is an 8-bit input port that can be read as general purpose inputs and is also used for the following functions:

| 11: | NMI  | Nonmaskable Interrupt Input          |

|-----|------|--------------------------------------|

| 12: | INT2 | Maskable Interrupt/Input Capture/URD |

| 13: | INT3 | Maskable Interrupt/Input Capture/UWR |

| 14: | INT4 | Maskable Interrupt/Input Capture     |

| 15: | SI   | MICROWIRE/PLUS Data Input            |

| 16: | RDX  | UART Data Input                      |

| 17: |      | •                                    |

Port D is an 8-bit input port that can be used as general purpose digital inputs.

Port P is a 4-bit output port that can be used as general purpose data, or selected to be controlled by timers 4

#### Pin Descriptions (Continued)

through 7 in order to generate frequency, duty cycle and pulse width modulated outputs.

#### **POWER SUPPLY PINS**

V<sub>PP</sub> Programming Power

V<sub>CC1</sub> Positive Power Supply

GND Ground for On-Chip Logic

DGND Ground for Output Buffers

Note: GND and DGND are electrically connected in the package. Both  $V_{CC}$  pins and both ground pins must be used.

#### **CLOCK PINS**

CKI The Chip System Clock Input

CKO The Chip System Clock Output (inversion of CKI)

Pins CKI and CKO are usually connected across an external

crystal.

CK2 Clock Output (CKI divided by 2)

#### **OTHER PINS**

WO This is an active low open drain output that signals an illegal situation has been detected by the Watch Dog logic.

ST1 Bus Cycle Status Output: indicates first opcode

ST2 Bus Cycle Status Output: indicates machine states (skip, interrupt and first instruction cycle).

RESET is an active low input that forces the chip to restart and sets the ports in a TRI-STATE® mode.

RDY/HLD has two uses, selected by a software bit. It's either a READY input to extend the bus cycle for slower memories, or a HOLD request input to put the bus in a high impedance state for DMA purposes.

EXM External memory enable (active high) disables internal EPROM and maps it to external memory.

El External interrupt with vector address FFF1:FFF0. (Rising/falling edge or high/low level sensitive). Alternately can be configured as 4th input capture.

EXUI External interrupt which is internally OR'ed with the UART interrupt with vector address FFF3:FFF2 (Active Low).

Places part in EPROM Programming mode (Active Low).

#### **Connection Diagrams**

TL/DD/10105-15

**Top View**

The HPC46083MH is a two chip system packaged in a dual cavity ceramic LDCC package, with a UV quartz window on bottom. Within the package is an HPC46083 and a UV-erasable EPROM with port recreation logic. Code executes out of the EPROM. The HPC46083MH may be programmed using a programming card to adapt the part to a 27C64 EPROM programmer. The part functions as the normal HPC, and the use of the EPROM should be transparent to the user. The only system design consideration is that pin 5 is  $V_{PP}$ , not  $V_{CC}$ , and should be tied to  $V_{CC}$  during normal operation. Pin 26 should also be tied to  $V_{CC}$ . DGND is connected internally to  $V_{SS}$  via a ground plane internal to the package. This should not cause any functional problems to a normal user of the part. Please be careful when inserting the part that the polarity dot is on pin 1.

When programming the part, care should be taken to use only the NSC HPC-EMU-PRGM 980420174 Programming card. This is easily distinguished by the large Yamaichi socket on the top. When programming it in the NSC MOLE Brain Board programmer be sure to use the Chip 2764 option in the programming menu. Use 13.5V  $\pm 0.5$ V for Vpp. The part will program in most 27C64 EPROM programmers, however refer to the data sheet to ensure that all timing requirements are met in the programming algorithm. Normal erase times under a UV light run about 45 mins., but may vary depending on the intensity of the light.

Suggested sockets and extractor tool:

Socket # AMP PLCC #821574-1

#6141749

YAMAICHI IC51-0684-390

IC120-0684-204

ENPLAS PLCC-68-1.27-02

Extractor Tool # AMP 821566-1

#### **Programming Information**

DC Electrical Characteristics  $T_A = 25 \pm 5^{\circ}C$ ,  $V_{CC} = 5.50V \pm 5\%$ ,  $V_{PP} = 13.5 \pm 0.5V$

| Symbol          | Parameter                                                                                  | Min | Max | Units |

|-----------------|--------------------------------------------------------------------------------------------|-----|-----|-------|

| I <sub>PP</sub> | V <sub>PP</sub> Supply Current during<br>Programming Pulse<br>RESET = CE = V <sub>IL</sub> |     | 60  | mA    |

| lcc             | V <sub>PP</sub> Supply Current                                                             |     | 35  | mA    |

Note 1: VCC must be applied either coincidentally or before Vpp and removed either coincidentally or after Vpp.

Note 2: Vpp must not be greater than 14V including overshoot. During  $\overline{CE} = B11 = V_{IL}$ ,  $V_{PP}$  must not be switched from 5V to 13.5V or vice-versa.

Note 3: During power up the B11 pin must be brought high (≥V<sub>IH</sub>) either coincident with or before power is applied to V<sub>PP</sub>.

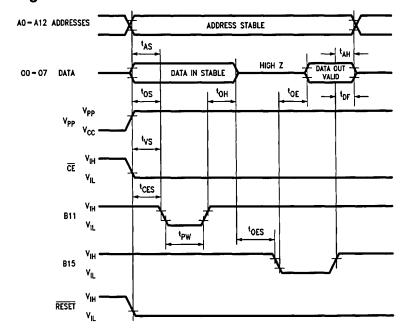

## AC Electrical Characteristics $T_A = 25 \pm 5^{\circ}C$ , $V_{CC} = 5.50V \pm 5\%$ , $V_{PP} = 13.5 \pm 0.5V$

| Symbol           | Parameter                              | Min | Тур | Max | Units |

|------------------|----------------------------------------|-----|-----|-----|-------|

| t <sub>AS</sub>  | Address Setup Time                     | 2   |     |     | μs    |

| t <sub>CES</sub> | CE Enable Setup Time                   | 2   |     |     | μs    |

| toes             | B <sub>11</sub> Enable Setup Time      | 2   |     |     | μs    |

| tos              | Data Setup Time                        | 2   |     |     | μs    |

| t <sub>AH</sub>  | Address Hold Time                      | 0   |     |     | μs    |

| t <sub>OH</sub>  | Data Hold Time                         | 2   |     |     | μs    |

| t <sub>DF</sub>  | Chip Disable to Output Float Delay     | 0   |     | 130 | ns    |

| toE              | Data Valid from B <sub>11</sub> Enable |     | -   | 130 | ns    |

| tvs              | V <sub>PP</sub> Setup Time             | 2   |     |     | μs    |

| tpw              | B <sub>15</sub> Pulse Width            | 1   | 5   | 10  | ms    |

# **Programming Waveform**

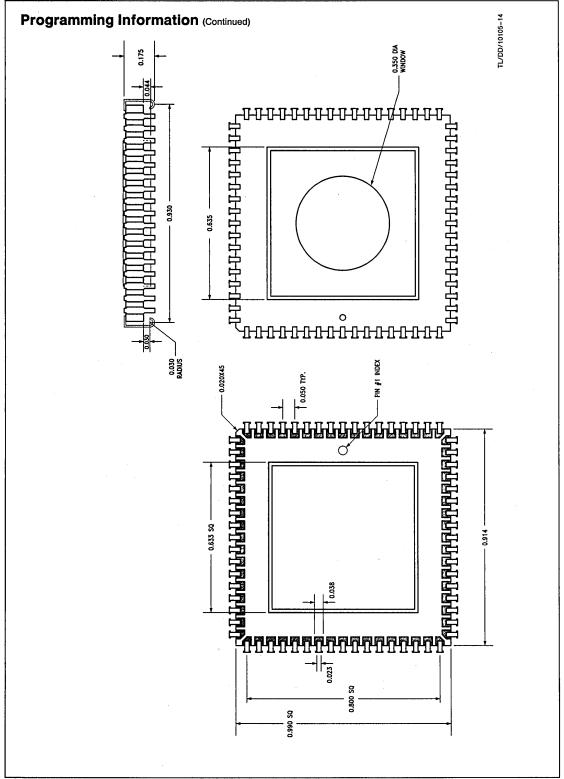

## **Programming Information (Continued)**

The following is the pin-connection list for programming the HPC Emulator.

| HPC EMU |                  | 27C64 |                 |

|---------|------------------|-------|-----------------|

| Pin     | Name             | Pin   | Name            |

| 1-4     | B0-B2, EXUI      | 28    | V <sub>CC</sub> |

| 5       | V <sub>PP</sub>  | 1     | V <sub>PP</sub> |

| 6       | 12               | 17    | O5              |

| 7       | 13               | 18    | O6              |

| 8       | 14               | 26    | NC              |

| 9-20    | 15-17, D0-D7, EI | 28    | Vcc             |

| 21      | EXM              | 16    | 04              |

| 22-25   | P0-P3            | NC    |                 |

| 26      | CE               | 20    | CE              |

| 27      | B15              | 22    | ŌĒ              |

| 28-30   | B12-B14          | 14    | GND             |

| 31      | B11              | 27    | PGM             |

| 32      | B10              | 15    | O3              |

| 33,34   | B9,B8            | 28    | Vcc             |

| 35      | A15              | 13    | O2              |

| 36      | A14              | 12    | O1              |

| 37      | A13              | 11    | 00              |

| HPC EMU |                   | 27C64         |       |

|---------|-------------------|---------------|-------|

| Pin     | Name              | Pin           | Name  |

| 38      | A12               | 2             | A12   |

| 39      | A11               | 23            | A11   |

| 40      | A10               | 21            | A10   |

| 41      | A9                | 24            | A9    |

| 42      | A8                | 25            | A8    |

| 43      | l v <sub>cc</sub> | 28            | Vcc   |

| 44      | DGND              | 14            | GND   |

| 45      | CK2               | NC            |       |

| 46      | RDY/HLD           | 19            | 07    |

| 47-54   | A7-A0             | 3-10          | A7~A0 |

| 55      | RESET             | 14            | GND   |

| 56,57   | ST1,ST2           | NC            |       |

| 58,59   | 10,11             | 28            | Vcc   |

| 60,61   | ско,скі           | Clock Circuit | NC    |

| 62      | GND               | 14            | GND   |

| 63      | wo                |               | NC    |

| 64-68   | B3-B7             | 28            | Vcc   |

Attach a crystal circuit to CKI & CKO.

#### Programming Hookup to Program as 27C64