# HS7067/HS7107 7 Amp, Multimode, High Efficiency Switching Regulator

# **General Description**

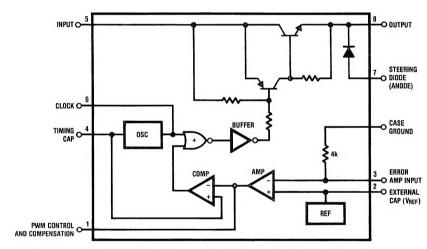

The HS7067/HS7107 is a hybrid high efficiency switching regulator with high output current capability. The device is housed in a standard TO-3 package containing a temperature compensated voltage reference, a pulse-width modulator with programmable oscillator frequency, error amplifier, high current, high voltage output switch and steering diode. The HS7067/HS7107 operates in a step-down, inverting, as well as in a transformer-coupled mode.

The HS7067/HS7107 can supply up to 7A of continuous output current over a wide range of input and output voltages.

#### **Features**

- HS7067—10V to 60V input

- HS7107—10V to 100V input

- 7A continuous output current

- Step-down, inverting, and transformer-coupled operation

- Frequency adjustable to 200 kHz

- High-efficiency (>75%)

- Standard 8-pin TO-3 package

# **Block and Connection Diagrams**

TL/K/6746-1

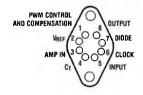

#### Metal Can Package

TL/K/6746-2

Top View Case is ground

Order Number HS7067CK, HS7067K, HS7107CK or HS7107K See NS Package Number K08A

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

V<sub>IN</sub>, Input Voltage

HS7067 65V HS7107 105V

IOUT, Output Current T<sub>J</sub>, Operating Temperature

150°C PD, Internal Power Dissipation 25W T<sub>A</sub>, Operating Temperature Range

HS7067C/7107C HS7067/7107

-55°C to +125°C --65°C to +150°C T<sub>STG</sub>, Storage Temperature Range

$V_{R}(V_{8-7}),$

Steering Diode Reverse Voltage

$I_{D}(I_{7-8}),$

88

Steering Diode Forward Current

105V 88

-25°C to +85°C

# **Electrical Characteristics** $T_C = 25^{\circ}C$ , $V_{IN} = 20V$ (unless otherwise specified)

| Symbol                                      | Parameter                                          |                                | Conditions                            |        | Min | Тур   | Max | Units    |

|---------------------------------------------|----------------------------------------------------|--------------------------------|---------------------------------------|--------|-----|-------|-----|----------|

| V <sub>IN</sub> -V <sub>OUT</sub>           | Min V <sub>IN</sub> /V <sub>OUT</sub> Differential | HS7067                         | $10V \le V_{IN} \le V_{IN(MAX)}$      |        |     | 3.0   |     | ٧        |

|                                             |                                                    | HS7107                         | I <sub>OUT</sub> = 2A (Note 6)        |        |     | 3.0   |     | ٧        |

| V <sub>S</sub>                              | Switch Saturation Voltage                          |                                | $I_C = 7.0A, V_{IN} = 10V$            | HS7107 |     | 1.6   | TBD | ٧        |

|                                             |                                                    |                                |                                       | HS7607 |     |       | 1.9 | ٧        |

|                                             |                                                    |                                | $I_{C} = 2.0A, V_{IN} = 10V$          |        |     | 1.0   |     | >        |

| V <sub>F</sub> Steering Diode On Voltage    |                                                    |                                | I <sub>D</sub> = 7.0A                 | HS7107 |     | 1.3   | TBD | <b>V</b> |

|                                             |                                                    |                                |                                       | HS7607 |     | , 1.7 | TBD |          |

|                                             |                                                    |                                | I <sub>D</sub> = 2.0A                 |        |     | 0.9   |     | >        |

| V <sub>IN</sub>                             | Supply Voltage Range                               | HS7067                         | $T_{MIN} \le T_A \le T_{MAX}$         |        | 10  |       | 60  | >        |

|                                             | (Note 7)                                           | HS7107                         | $T_{MIN} \le T_A \le T_{MAX}$         |        | 10  |       | 100 | >        |

| I <sub>R</sub>                              | Steering Diode Reverse Current                     |                                | V <sub>R</sub> = 100V                 |        |     |       | 60  | μΑ       |

| IQ                                          | Quiescent Current (Note 3)                         |                                | 0% Duty Cycle (V <sub>3</sub> = 3.0   | 0V)    |     | 6     |     | mA       |

|                                             |                                                    |                                | 100% Duty Cycle (V <sub>3</sub> = 0V) |        |     | 26    |     | mA       |

| V <sub>2</sub>                              | Reference Voltage on Pin 2                         |                                | $T_{MIN} \le T_A \le T_{MAX}$         |        | 2.3 | 2.5   | 2.7 | <b>V</b> |

| V <sub>CLK H</sub>                          | Clock Output High                                  |                                | $I_{CLK} = -750 \mu\text{A}$          |        | 1.2 | 1.6   |     | >        |

| V <sub>CLK L</sub>                          | Clock Output Low                                   |                                | I <sub>CLK</sub> = 80 μA              |        |     |       | 0.9 | >        |

| $\Delta V_2$                                | Line Regulation of<br>Reference Voltage on Pin 2   |                                | $V_{MIN} \le V_{IN} \le V_{MAX}$      |        |     | 5     |     | m۷       |

| R <sub>A</sub>                              | Resistance on Pin 3 to Ground (Note 4)             |                                | (Note 4)                              |        |     | 4.0   |     | kΩ       |

| V <sub>OUT</sub>                            | Feedback Resistor Rf Tol. ±                        | 1%                             |                                       | HS7107 |     | 4     | TBD | %        |

|                                             |                                                    |                                |                                       | HS7067 |     |       | 9   |          |

| V <sub>4</sub>                              | Voltage Swing—Pin 4                                |                                |                                       |        |     | 3.0   |     | >        |

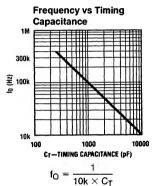

| l <sub>4</sub>                              | Charging Current—Pin 4                             |                                |                                       |        |     | 330   |     | μΑ       |

| ICLK                                        | Clock Input Current — Pin 6                        |                                | V <sub>CLK</sub> = 3.5V               |        |     | 1.75  | 4   | mA       |

| t <sub>r</sub>                              | Transistor Current Rise Time                       |                                | I <sub>O</sub> = 2.0A (Note 6)        |        |     | 70    |     | ns       |

|                                             |                                                    |                                | I <sub>O</sub> = 7.0A (Note 6)        |        |     | 120   |     | ns       |

| t <sub>f</sub> Transistor Current Fall Time |                                                    | I <sub>O</sub> = 2.0A (Note 6) |                                       |        | 100 |       | ns  |          |

|                                             |                                                    |                                | I <sub>O</sub> = 7.0A (Note 6)        |        |     | 160   |     | ns       |

| ts                                          | Diode Storage Time                                 |                                | I <sub>O</sub> = 7.0A (Note 6)        |        |     | 120   |     | ns       |

| t <sub>d</sub>                              | Delay Time                                         |                                | I <sub>O</sub> = 7.0A (Note 6)        |        |     | 600   |     | ns       |

| f <sub>MAX</sub>                            | Max Clock Frequency                                |                                | (Note 5)                              |        |     |       | 200 | kHz      |

# $\textbf{Electrical Characteristics} \ \textbf{T}_{C} = 25^{\circ} \text{C, V}_{IN} = 20 \text{V (unless otherwise specified) (Continued)}$

| Symbol             | Parameter          | Conditions            |                                   | Min | Тур | Max | Units |

|--------------------|--------------------|-----------------------|-----------------------------------|-----|-----|-----|-------|

| Z <sub>PIN 1</sub> | Impedance at Pin 1 | (Note 6)              |                                   |     | 5   |     | МΩ    |

| η                  | Efficiency         | $V_{OUT} = 5V$        | f <sub>O</sub> = 25 kHz (Note 6)  |     | 80  |     | %     |

|                    |                    | I <sub>OUT</sub> = 1A | f <sub>O</sub> = 200 kHz (Note 5) |     | 70  |     | %     |

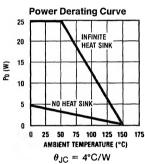

| $\theta_{\sf JC}$  | Thermal Resistance | (Note 1)              |                                   |     | 4.0 |     | °C/W  |

Note 1:  $\theta_{JA}$  is typically 35°C/W for natural convection cooling.

Note 2: VOUT and IOUT refer to the output DC voltage and output current of a switching supply after the output LC filter as shown in Figure 1.

Note 3: Quiescent current depends on the duty cycle of the switching translator.

Note 4: This test includes the input bias current of the error amplifier.

Note 5: Circuit configured as shown in Figure 1.

Note 6: These parameters are not tested. They are given for informational purposes only.

Note 7: Functionally tested at limits only (pass-fail).

# **Typical Performance Characteristics**

# **Typical Applications**

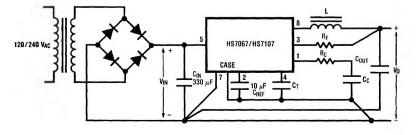

### THE BUCK CONVERTER (Step Down)

The buck converter is the most common application in switching-power conversion. It allows to step down a voltage with a minimum of components and a maximum of efficiency (for further information on the theory of operation of a buck converter, see AN-343).

| fo               | 25 kHz    | 200 kHz  |

|------------------|-----------|----------|

| L                | 86 μH     | 21 μΗ    |

| C <sub>T</sub>   | 0.0039 μF | 330 pF   |

| СС               | 0.2 μF    | 0.068 μF |

| R <sub>f</sub>   | 4 kΩ      | 4 kΩ     |

| R <sub>C</sub>   | 5.7 kΩ    | 5.7 kΩ   |

| C <sub>OUT</sub> | 1500 μF   | 680 μF   |

$V_{\text{IN}} = 10V \text{ to } 35V$

$V_{OUT} = 5V$

IOUT = 1A to 6A

Load Regulation = 40 mV Line Regulation = 5 mV

TL/K/6746-4

Design equations:

Following are the design equations for a buck converter application using the HS 7107/7067:

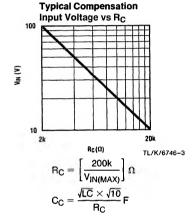

$$\begin{split} C_T &= \frac{1}{10^4 \times f_O} \\ L_{MIN} &= \frac{(V_{IN(MAX)} - V_O) V_O}{V_{IN(MAX)} \times f_O \times \Delta I} \qquad \text{(Note 7, 9)} \\ C_{MIN} &= \frac{\Delta I}{4 \, f_O \, (e_O - \Delta I \times ESR)} \qquad \text{(Note 8, 9)} \\ C_C &= \frac{\sqrt{10 \, LC}}{R_C} \\ R_C &= \frac{2 \times 10^5}{V_{IN(MAX)}} \\ R_f &= 4 k \Big(\frac{V_O - 2.5}{2.5}\Big) \Omega \end{split}$$

Note 7: L<sub>MIN</sub> is the minimum value of output filter inductance, L, for stable operation.

Note 8: C<sub>MIN</sub> is the minimum value of output filter capacitance, C, necessary to achieve an output ripple voltage, e<sub>O</sub>. ESR is the Effective Series Resistance of the output filter capacitor, C, at the operating frequency, f<sub>O</sub>.

Note 9:  $\Delta I = \text{Peak to Peak Ripple current through the inductor and the capacitor.} \ \frac{\Delta I}{2} < I_{O \, MIN} \, \text{and} \, \frac{\Delta I}{2} < 7 - I_{O \, MAX}.$

#### **Efficiency Equations**

Since high efficiency is the principal advantage of switchedmode power conversion, switching regulator losses are an important design concern. Losses and efficiency of a buck converter can be calculated with the following equations.

Note: Pin 7 is grounded;  $I_0$  = average output current at pin 8

Switching Period (T)

$$T = \frac{1}{f_0} = t_{ON} + t_{OFF}$$

Duty Cycle (D)

$$D = \frac{t_{ON}}{t_{ON} + t_{OFF}} = \frac{V_O + V_F}{V_{IN} - V_S + V_F}$$

Transistor DC Losses (PT)

$$P_T = V_S \times I_O \times D$$

Transistor Switching Losses (PS)

$$P_S = (V_{IN} + V_F) \times I_O \times \frac{(t_r + t_f + 2t_S) f_O}{2}$$

Capacitor Losses (Pc)

$$P_{C} = ESR \times \left(\frac{V_{O} (T - DT)}{4L}\right)^{2}$$

Diode DC Losses (PD)

$$P_D = V_f \times I_O \times (1 - D)$$

Drive Circuit Losses (DL)

$$D_L = 0.02 \times V_{IN} \times D$$

Inductor Losses (PL)

$$P_L = I_O^2 \times R_L$$

(DC winding resistance)

Power Output (PO)

$$P_{O} = \frac{((V_{IN} - V_{S}) t_{ON}) - ((V_{F}) t_{OFF})}{t_{ON} + t_{OFF}} \times I_{O}$$

Efficiency (η)

$$\eta = \frac{P_{O}}{P_{IN}} = \frac{P_{O}}{P_{O} + P_{T} + P_{S} + P_{D} + D_{L} + P_{L} + P_{C}}$$

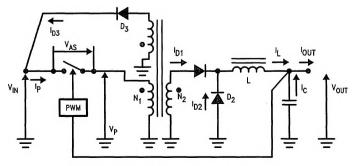

#### TRANSFORMER COUPLED CONVERTERS

In addition to the implementation of a buck converter, the HS 7107/7067 can be used in various transformer coupled configurations. They can be used in various topologies such as: step-up, step-down, inverter, multiple outputs and isolated converters.

There are basically two different methods in implementing transformer coupled converters: the flyback and the foward topology

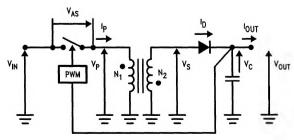

#### The Flyback Principle

Figure 1 shows a functional diagram of a flyback converter. Depending on the turn ratio N2/N1 and the feedback voltage, it can be implemented as a step-down or step-up converter.

When the switch is on, the current  $(I_p)$  flows through the primary winding creating a magnetic flux in the core and storing the energy. At this time, the voltage at the secondary keeps the same polarity (with respect to the dotted terminals), the diode is off and no current flows through it. When the switch is off, the voltage at the secondary and primary becomes reversed and the diode turns-on  $(I_d)$ . The stored energy is then transferred to the load and the output filter capacitor. The energy stored in the capacitor will supply the load current during the next turn-on.

FIGURE 1. Typical Flyback Functional Diagram

TL/K/6746-5

$V_p$  = Voltage at primary

V<sub>as</sub> = Voltage across the switch

V<sub>s</sub> = Voltage at the secondary

Ip = Current at primary

I<sub>d</sub> = Current through diode

= Current through output cap

I<sub>out</sub> = Output current of the converter

ΔI = Ripple current

lc

$D = T_{on}/(T_{off} + T_{on})$

F = Switching frequency

V<sub>df</sub> = Forward voltage drop of the diode

$V_1 = V_{out} \times N_1/N_2$   $V_2 = V_{in} + V_{out} N_1/N_2$

V<sub>3</sub> = Saturation voltage of the switch

$V_4 = V_{out} + V_{d1}$   $V_5 = V_{in} \times N_2/N_1$

TL/K/6746-6

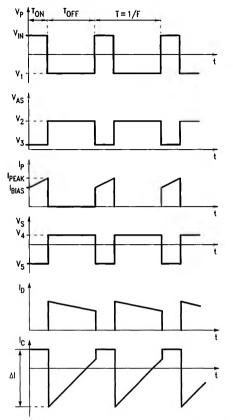

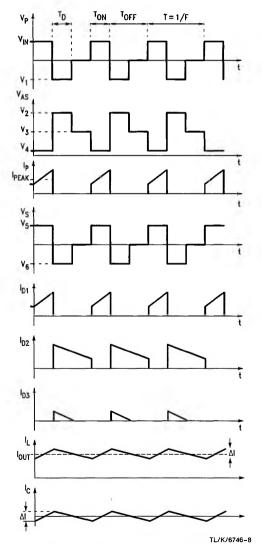

FIGURE 2. Typical Flyback Waveforms

The load current is not supplied directly by the input source when the switch is on, but only by the energy stored in the output capacitor. The output voltage is monitored by the feedback loop which controls the duty cycle (D) through the PWM (Pulse Width Modulator) which in turn, modulates the amount of energy being transferred from the input to the output. Figure 2 shows the waveforms of a continuous mode flyback converter (primary current  $I_{\rm D}$  is DC biased).

#### The Forward Principle

The forward converter is a little more complex and requires more components than the flyback, but the output ripple voltage is smaller. *Figure 3* shows a simplified diagram of a forward converter.

When the switch turns-on, a voltage  $V_5 = V_1 \times N_2/N_1$  appears at the secondary of the transformer. The diode  $D_2$

FIGURE 3. Typical Forward Functional Diagram

TL/K/6746-7

is off while D<sub>1</sub> turns-on, allowing the current to flow through the inductor L (Id1 and II), storing energy in its core, and supplying the load current (lout) and the capacitor current (Ic) at the same time. When the switch turns-off, the magnetic energy stored in the core of the inductor creates a current (Id2) which flows through the diode D2. The load current lout therefore, equals to Id2 + Ic.

During the "off" time of the switch, some residual magnetism will stay in the core of the transformer and has to be removed before the next cycle, so that it does not accumulate, leading to core saturation.

A demagnetizing winding is used to "dump" the residual energy back to the input or output of the converter. The functional principle of the demagnetizing winding is similar to the flyback in the sense that, during the turn-off time, the residual magnetism will generate a reverse voltage at the demagnetizing winding (with respect to the dotted terminals) turning on the diode D<sub>3</sub>.

In the forward mode, when the switch is off, the load current is supplied by the energy stored in the output capacitor and the choke inductor but when the switch is on, it is supplied by the input source through the transformer. This accounts for the lower output ripple voltage.

The output voltage is monitored by the feedback loop, which controls the duty cycle through the PWM, which in turn modulates the amount of energy being transferred from the input to the output.

= Voltage across the switch = Voltage at secondary = Current at primary = Current through diode D<sub>1</sub> ldi = Current through diode D₂ las = Current through diode Da laa = Current through inductor L IL. = Current through output cap = Output current of the converter  $\Delta_1$ = Ripple current = Switching frequency D  $= T_{on} / (T_{off} + T_{on})$  $=V_{in}\times N_1/N_3$ ٧٥  $= V_{in} + V_1$ = Saturation voltage of the switch

$= V_{in} \times N_2/N_1$

= Voltage at primary

$V_6 = V_{in} \times N_2/N_3$ Figure 4 shows the waveforms of the forward converter.

When the switch is off,  $V_{as}=V_{in}+(V_{in}\times N_1/N_3)$  during the demagnetization time (T<sub>d</sub>) and then, drops to  $V_{as}=V_{in}$ as indicated in Figure 4.

FIGURE 4. Typical Forward Waveforms

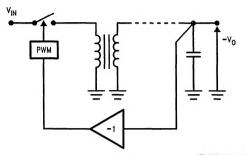

With both flyback and forward topologies, it is possible to design an inverting converter by using an external op-amp (Figure 5).

TL/K/6746-10

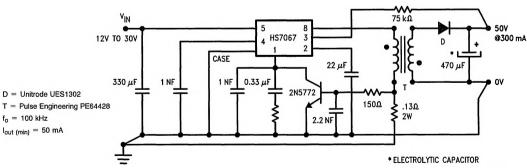

#### Flyback Step-Up Application

Figure 6 shows flyback converter in a step-up mode where an input voltage of +12V to +30V will be converted into a regulated output voltage of +50V.

#### Performance Data

| Parameter       | Conditions                                                                    | Result |

|-----------------|-------------------------------------------------------------------------------|--------|

| Efficiency      | V <sub>out</sub> = 50V @300 mA<br>V <sub>in</sub> = 15V                       | 82%    |

| Line Regulation | $V_{out} = 50V @300 \text{ mA}$<br>12V $\leq V_{in} \leq 30V$                 | 0.2%   |

| Load Regulation | $V_{in} = 15V$ $V_{out} = 50V$ $50 \text{ mA} \le I_{out} \le 300 \text{ mA}$ | 0.2%   |

#### **Isolated Flyback Converter**

Figure 7 shows an isolated flyback converter using a sense winding for feedback. Although, in practice the line regulation is acceptable, the load regulation can be marginal if the coupling between the windings is poor. However, the sense winding cannot detect any ohmic voltage drop in the main output so, a heavier gauge wire should be used to reduce this regulation error. Also, the sense winding will not sense the non-linear voltage drop across the diode, and this accounts for most of the load regulation inaccuracy. Therefore, the sense winding method is only recommended for applications where load variations are small.

Figure 7 shows an isolated flyback converter with an output of 5V at 2A. The input voltage range is from +10V to +40V. The output can be adjusted to +5V by using the 5 k $\Omega$  trimpot.

#### **Performance Data**

| Parameter       | Conditions                                          | Result |

|-----------------|-----------------------------------------------------|--------|

| Efficiency      | V <sub>out</sub> = 5V @ 2A<br>V <sub>in</sub> = 30V | 75%    |

| Line Regulation | $V_{out} = 5V @ 2A$<br>$10V \le V_{in} \le 40V$     | 5%     |

| Load Regulation | $V_{in} = 30V$<br>$1A \le I_{out} \le 2A$           | 7%     |

#### **Isolated Forward Converter**

As described previously, forward converters exhibit lower output ripple voltage and the opto-coupler feedback scheme provides good regulation as well as input to output isolation.

An opto-coupler feedback is usually difficult to implement because the transfer function of the opto-coupler is non-linear, the current transfer ratio changes with time and temperture and also from one unit to another. Figure 8 shows the circuit diagram of a 5V @ 3A power converter with an input voltage range of +14V to +30V using an isolated forward topology.

TL/K/6746-11

A 12V to 60V input Voltage Range is possible by replacing the HS7067 with a HS7107. The converter will operate in a discontinuous mode above 30V with a 300 mA load (the transformer's secondary current drops to zero before the switch turns on) and therefore, may generate more switching noise.

FIGURE 6. Flyback Step-Up Converter

#### **Typical Applications** (Continued) = International Rectifier 50SQ060 D<sub>2</sub> l<sub>out (min)</sub> = 1A fo = 100 kHz = Transformer made of a core Fenoxcube 1811PA2503B7 = 8 turns with 5 strands #29 Secondary = 6 turns with 15 strands #30 = 25 turns with 1 strand #30 Sense windings should be interleaved in order to improve 10 kΩ 100 the coupling and regulation. 8 10V TO 40V HS7067 22 μF CASE 330 μF 1 NF 0.33 µF 2N5772 150Ω 2W \* ELECTROLYTIC CAPACITOR FIGURE 7. Isolated Flyback Converter TL/K/6746-12 = D<sub>2</sub> = International Rectifier 50SQ060 $D_3$ = Unitrode UES1302 = Pulse Engineering PE64423 Т = Pulse Engineering PE52711 = 50 kHz fo $I_{out (min)} = 0.5A$ 14V TO 30V HS7067 @3A CASE 3300 µF 330 μF 2 NF 120Ω LM 340 LAH - 5 3 kΩ **≶** 15 kΩ 150Ω 0.01 µF .13Ω 22 NF 45.3 kΩ 470 kΩ 4N27 \* ELECTROLYTIC CAPACITOR FIGURE 8a. Isolated Forward Converter TL/K/6746-13 TL/K/6746-9 Figure 8b shows the typical forward converter waveforms in continuous mode which can be observed using the circuit from Figure 8a. Top waveform is the voltage

across the switch (20V/div). Bottom waveform is the current throughout the switch (1A/dv). Horizontal Scale = 5 μS/dir. V<sub>in</sub> = 20V; V<sub>out</sub> = 5V @ 3A. **Figure 8b.**

An LM 385z (adjustable reference) is used as a comparator and error amplifier. This reference always wants to maintain 1.2V between pins 1 and 2 and will draw as much current as necessary from the opto-coupler to achieve this. Therefore, the feedback loop is virtually independent of the gain of the opto-coupler.

#### Performance Data

| Parameter       | Conditions                                              | Result |

|-----------------|---------------------------------------------------------|--------|

| Efficiency      | V <sub>out</sub> = 5V @ 3A<br>V <sub>in</sub> = 30V     | 78%    |

| Line Regulation | $V_{out} = 5V @ 3A$<br>14V $\leq V_{in} \leq 30V$       | 0.1%   |

| Load Regulation | $V_{out} = 5V$ $V_{in} = 20V$ $0.5A \le I_{out} \le 3A$ | 0.1%   |

#### **Isolated Telecom Converter**

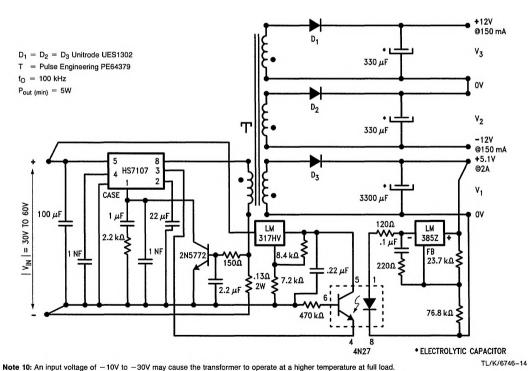

Figure 9 shows an isolated triple output converter which will transform a positive or negative input voltage of 32V to 60V to an uncommitted triple output of +12V, -12V, and 5V, which may be later referenced to the system ground. This converter is ideal for a step down converter of high positive voltage or high negative voltage such as -48V used in telecom circuits.

#### Performance Data

| Parameter                                                               | Conditions                                                                                                                                                | Result |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Efficiency                                                              | V <sub>1</sub> = 5.1V @ 2A<br>V <sub>2</sub> = -12V @ 150 mA<br>V <sub>3</sub> = 12V @ 100 mA<br> V <sub>in</sub>   = 48V                                 | 62%    |

| Line Regulation<br>on Main Secondary                                    | $40V \le  V_{in}  \le 60V$<br>$V_1 = 5.1V @ 2A$<br>$V_2 = -12V @ 150 mA$<br>$V_3 = +12V @ 150 mA$                                                         | 0.8%   |

| Load Regulation on Main Secondary                                       | $\begin{aligned}  V_{in}  &= 48V \\ V_1 &= 5.1V \\ V_2 &= 12V @ 150 \text{ mA} \\ V_3 &= 12V @ 150 \text{ mA} \\ 0.5 &\leq I_{out} \leq 2A \end{aligned}$ | 1%     |

| Load Regulation<br>on 12V Secondary<br>for Simultaneous<br>Load Changes | $ V_{in}  = 48V$<br>$V_1 = 5.1V @ 2A$<br>$V_2 = -12V$<br>$V_3 = 12V$<br>$75 \text{ mA} \le I_{out} \le 150 \text{ mA}$                                    | 5%     |

# **Application Hints**

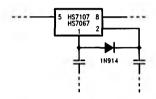

#### **DUTY CYCLE LIMITING**

In a flyback converter, the error amplifier sees 0V at the output of the converter during the initial turn-on, and forces the duty cycle to 100% until it sees the output voltage rising to the final value; but no voltage will appear if the switch does not turn off (see flyback principle). The result is that the core will saturate, reducing the effective impedance of the transformer to about  $0\Omega$ , and destroying the pass transistor. To prevent this, the duty cycle must be limited to a value at which the core does not saturate. A diode connected between pins 1 and 2 (*Figure 10*), will limit the duty cycle to about 80%.

TL/K/6746-15

FIGURE 10. Duty Cycle Limiting Circuit

#### SOFT START

For any converter, connecting a large capacitor (20 to 200  $\mu$ F) between pin 2 and the case is recommended to allow the reference voltage to slowly reach its final value after start-up. This allows the HS 7067/7107 to start-up smoothly and minimizes the inrush current. The time constant can be calculated by:

$$T = 10^3 \times C$$

It is always a good practice to incorporate soft start and duty cycle limiting when designing a switching power converter, especially when a current limit circuitry is not utilized.

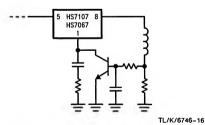

#### **CURRENT LIMIT**

The schematic in *Figure 11* shows how to protect the pass transistor against excessive current, by sensing the current through a series resistor, and shorting the PWM control voltage at pin 1 to ground, using transistor 2N5772 (this is made possible by the 5  $\rm M\Omega$  output impedance of the error amplifier), which will cause the pass transistor to turn off.

**FIGURE 11. Current Limit Circuitry**

The sense resistor should be a low inductance type, otherwise the series inductance creates a high impedance at transients and activates the shutdown circuitry. If such a resistor cannot be found, a 0.1  $\mu F$  connected in parallel with it will compensate the series inductance.

When such a circuitry is used, the duty cycle limiting diode becomes optional, but the soft start capacitor should still be at least 10  $\mu$ F.

#### **DECOUPLING AND GROUNDING**

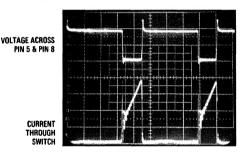

Special attention should be given to the decoupling of the HS 7107/7067 itself at the input (pin 5), where the capacitor must be at least 100  $\mu$ F and connected as close to the device as possible. Large switching spikes at the input of the pass transistor can cause breakdown of the junction and destroy the device. (See Figure 12.)

The waveform at the top of the picture represents the voltage across the switch of a typical BUCK (step down) converter. When the switch is turned off, the current in the inductor falls to zero (see waveform at the bottom) and a switching spike occurs across the switch. This spike can reach several tens of volts on top of the normally expected voltage across the switch and lead to stress on the device if the overall voltage exceeds the maximum rating.

The picture below shows a spike of about ten volts with a 330  $\mu$ F capacitor of average quality.

VERTICAL SCALE: 20 VOLTS/DIV HORIZONTAL SCALE: 2 µS/DIV

TL/K/6746-17

#### FIGURE 12

The reference voltage (pin 2) must be decoupled with at least 10  $\mu$ F and the compensation network (pin 1) should be decoupled with a ceramic capacitor of 1 nF to 10 nF. Switching noise on the reference voltage pin (pin 2) or on the compensation pin (pin 1) can create different types of oscillations and instabilities.

Because of the high current and high voltage capability of the HS 7107/7067 a single point grounding or, at least a grounding where the force ground is separated from the circuit ground, is highly recommended.

# **Ordering Information (Transformers and Inductors)**

PULSE ENGINEERING INC. 7250 Convoy Court San Diego, CA 92111 USA Tel: (619) 268-2400 TWX: 910-335-1527 FAX: 619 268-2515