# Ultra Low Input Bias Current INSTRUMENTATION AMPLIFIER

## **FEATURES**

- LOW INPUT BIAS CURRENT: 3fA typ

- BUFFERED GUARD DRIVE PINS

- LOW OFFSET VOLTAGE: 2mV max

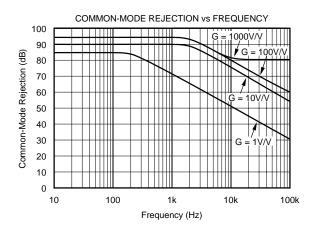

- HIGH COMMON-MODE REJECTION: 84dB (G = 10)

- LOW QUIESCENT CURRENT: 1mA

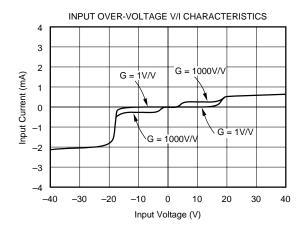

- INPUT OVER-VOLTAGE PROTECTION: ±40V

## **APPLICATIONS**

- LABORATORY INSTRUMENTATION

- pH MEASUREMENT

- ION-SPECIFIC PROBES

- LEAKAGE CURRENT MEASUREMENT

## DESCRIPTION

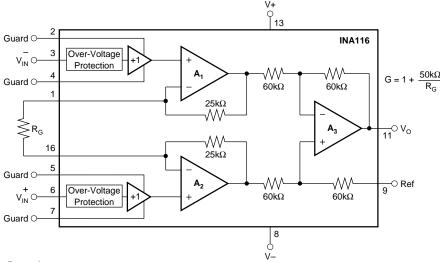

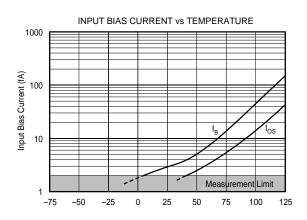

The INA116 is a complete monolithic FET-input instrumentation amplifier with extremely low input bias current. **Difet**® inputs and special guarding techniques yield input bias currents of 3fA at 25°C, and only 25fA at 85°C. Its 3-op amp topology allows gains to be set from 1 to 1000 by connecting a single external resistor.

Guard pins adjacent to both input connections can be used to drive circuit board and input cable guards to maintain extremely low input bias current.

The INA116 is available in 16-pin plastic DIP and SOL-16 surface-mount packages, specified for the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

Difet®; Burr-Brown Corporation

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

AT  $\rm T_A$  = +25°C,  $\rm V_S$  = ±15V,  $\rm R_L$  = 10k $\Omega$ , unless otherwise noted.

|                                                                                                                                                                                                                                                       |                                                                                                                                                   | INA116P, U            |                                                                                                                           |                                                                  | INA116PA, UA         |                                         |                                        |                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------|-----------------------------------------|----------------------------------------|-----------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                             | CONDITIONS                                                                                                                                        | MIN                   | TYP                                                                                                                       | MAX                                                              | MIN                  | TYP                                     | MAX                                    | UNITS                                                           |

| INPUT Offset Voltage, RTI Initial vs Temperature vs Power Supply Long-Term Stability Bias Current vs Temperature Offset Current vs Temperature Impedance, Differential Common-Mode Common-Mode Voltage Range Safe Input Voltage Common-Mode Rejection | $T_{A} = +25^{\circ}C$ $T_{A} = T_{MIN} \text{ to } T_{MAX}$ $V_{S} = \pm 4.5V \text{ to } \pm 18V$ $V_{CM} = \pm 11V, \ \Delta R_{S} = 1k\Omega$ | s                     | ±0.5 ±0.5/G ee Typical Curv ±10 ±15/G ±1 ±5/G ±3 ee Typical Curv = 1015/0.2 >1015/7 (V+)-2 (V-)+2.4                       | ±50 ±100/G<br>±25<br>re<br>±25                                   | *<br>*<br>*          | *****                                   | ±5 ±5/G<br>±100 ±200/G<br>±100<br>±100 | mV<br>μV/V<br>μV/mo<br>fA<br>fA<br>Ω/pF<br>Ω/pF<br>V<br>V       |

|                                                                                                                                                                                                                                                       | G = 1<br>G = 10<br>G = 100<br>$V_{CM} = \pm 5V, G = 1000$                                                                                         | 80<br>84<br>86<br>86  | 89<br>92<br>94<br>94                                                                                                      |                                                                  | 73<br>78<br>80<br>80 | *<br>*<br>*                             |                                        | dB<br>dB<br>dB<br>dB                                            |

| NOISE Voltage Noise, RTI $f = 1kHz$ $f_B = 0.1Hz$ to 10Hz Current Noise                                                                                                                                                                               | $G = 1000, R_S = 0\Omega$                                                                                                                         |                       | 28<br>2                                                                                                                   |                                                                  |                      | * *                                     |                                        | nV/√Hz<br>μVp-p<br>fA/√Hz                                       |

| f = 1kHz  GAIN  Gain Equation  Range of Gain  Gain Error  Gain vs Temperature <sup>(1)</sup> 50kΩ Resistance <sup>(1)(2)</sup> Nonlinearity                                                                                                           | G = 1<br>G = 10<br>G = 100<br>G = 1000<br>G = 1<br>G = 1<br>G = 10<br>G = 100<br>G = 1000                                                         | 1                     | 0.1<br>1+(50kΩ/R <sub>G</sub> )<br>±0.01<br>±0.25<br>±0.35<br>±1.25<br>±5<br>±25<br>±0.0005<br>±0.001<br>±0.001<br>±0.005 | 1000<br>±0.05<br>±0.4<br>±0.5<br>±10<br>±100<br>±0.005<br>±0.005 | *                    | * * * * * * * * * * * * * * * * * * * * | * 0.1 ±0.5 ±0.7  ±20 ±100 ±0.01 ±0.01  | V/V V/V % % % ppm/°C ppm/°C % of FSR % of FSR % of FSR % of FSR |

| GUARD OUTPUTS Offset Voltage Output Impedance Current Drive                                                                                                                                                                                           |                                                                                                                                                   |                       | ±15<br>650<br>+2/-0.05                                                                                                    | ±50                                                              |                      | *<br>*<br>*                             | *                                      | mV<br>Ω<br>mA                                                   |

| OUTPUT Voltage Positive Negative Load Capacitance Stability Short-Circuit Current                                                                                                                                                                     | $R_L = 10k\Omega$<br>$R_L = 10k\Omega$                                                                                                            | (V+) -1<br>(V-) +0.35 | (V+) -0.7<br>(V-) +0.2<br>1000<br>+5/-12                                                                                  |                                                                  | *                    | *<br>*<br>*<br>*                        |                                        | V<br>V<br>pF<br>mA                                              |

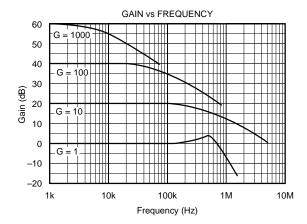

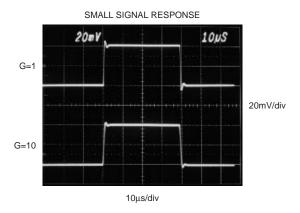

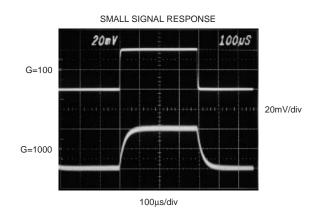

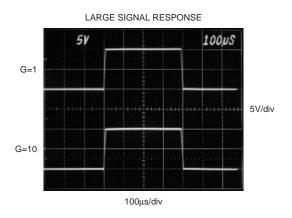

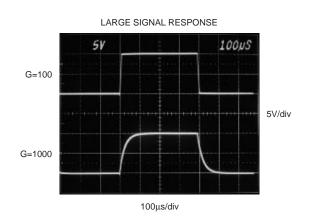

| FREQUENCY RESPONSE Bandwidth, -3dB  Slew Rate Settling Time, 0.01%  Output Overload Recovery                                                                                                                                                          | G = 1<br>G = 10<br>G = 100<br>G = 1000<br>G = 10 to 200<br>10V Step, G = 1<br>G = 10<br>G = 100<br>G = 1000<br>50% Overdrive                      |                       | 800<br>500<br>70<br>7<br>0.8<br>22<br>25<br>145<br>400<br>20                                                              |                                                                  |                      | * * * * * * * * * * * * * * * * * * * * |                                        | kHz<br>kHz<br>kHz<br>kHz<br>V/µs<br>µs<br>µs<br>µs              |

| POWER SUPPLY Voltage Range Current                                                                                                                                                                                                                    | V <sub>IN</sub> = 0V                                                                                                                              | ±4.5                  | ±15<br>±1                                                                                                                 | ±18<br>±1.4                                                      | *                    | * *                                     | *                                      | V<br>mA                                                         |

| TEMPERATURE RANGE Specification Operating $\theta_{\rm JA}$ Specification same as INA1 $^{\circ}$                                                                                                                                                     |                                                                                                                                                   | -40<br>-40            | 80                                                                                                                        | 85<br>125                                                        | *<br>*               | *                                       | * *                                    | °C<br>°C<br>°C/W                                                |

<sup>\*</sup> Specification same as INA116P

NOTE: (1) Guaranteed by wafer test. (2) Temperature coefficient of the " $50k\Omega$ " term in the gain equation.

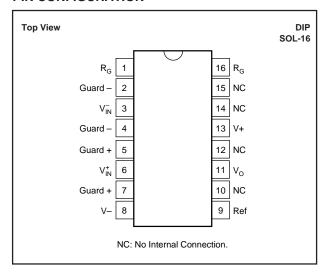

#### PIN CONFIGURATION

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage                    | ±18V           |

|-----------------------------------|----------------|

| Input Voltage Range               | ±40V           |

| Output Short-Circuit (to ground)  | Continuous     |

| Operating Temperature             | 40°C to +125°C |

| Storage Temperature               | 40°C to +125°C |

| Junction Temperature              | +150°C         |

| Lead Temperature (soldering, 10s) | +300°C         |

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## **PACKAGE INFORMATION**

| PRODUCT  | PACKAGE              | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|----------------------|------------------------------------------|

| INA116PA | 16-Pin Plastic DIP   | 180                                      |

| INA116P  | 16-Pin Plastic DIP   | 180                                      |

| INA116UA | SOL-16 Surface-Mount | 211                                      |

| INA116U  | SOL-16 Surface-Mount | 211                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

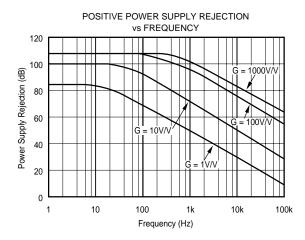

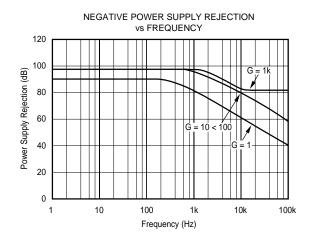

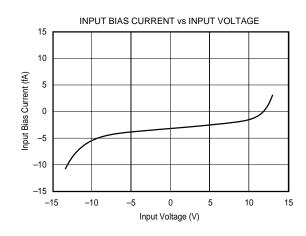

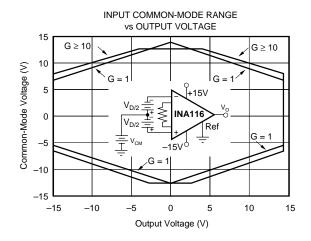

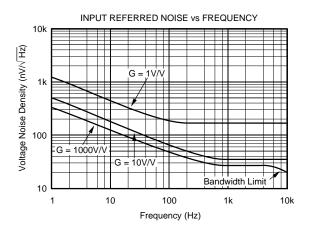

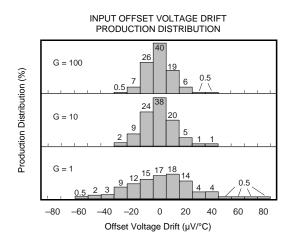

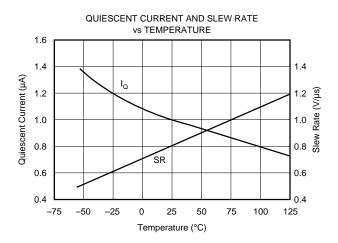

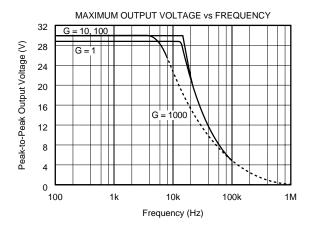

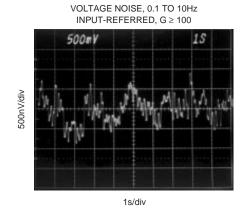

## **TYPICAL PERFORMANCE CURVES**

At  $T_A$  = +25°C,  $V_S$  = ±15V,  $R_L$  = 10k $\Omega$ , unless otherwise noted.

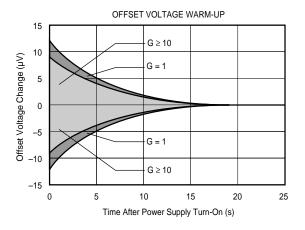

# TYPICAL PERFORMANCE CURVES (CONT)

At  $T_A$  = +25°C,  $V_S$  = ±15V,  $R_L$  = 10k $\Omega$ , unless otherwise noted.

# **TYPICAL PERFORMANCE CURVES (CONT)**

At  $T_A$  = +25°C,  $V_S$  = ±15V,  $R_L$  = 10k $\Omega$ , unless otherwise noted.

## APPLICATIONS INFORMATION

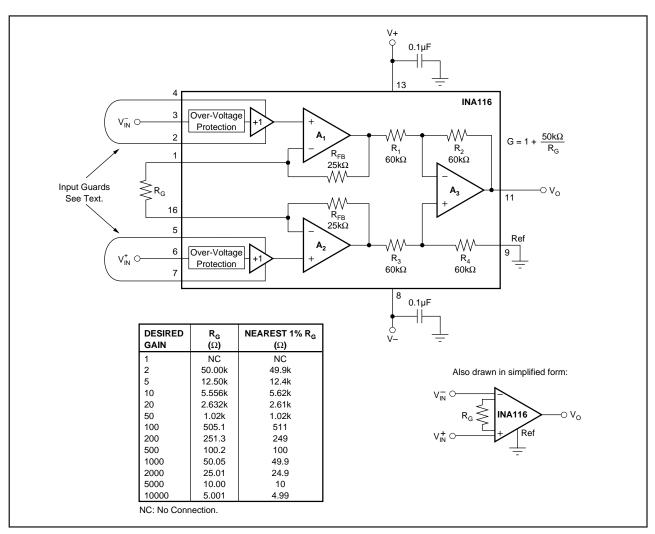

Figure 1 shows the connections required for basic operation of the INA116. Applications with noisy or high impedance power supplies may require decoupling capacitors close to the supply pins as shown.

The output is referred to the output reference (Ref) terminal which is normally grounded. This must be a low impedance connection to assure good common-mode rejection. A resistance of  $30\Omega$  in series with this connection will cause a typical device to degrade to approximately 72dB CMR at G=1.

#### **SETTING THE GAIN**

Gain of the INA116 is set by connecting a single external resistor,  $R_G$ , as shown. The gain is—

$$G = 1 + \frac{50k\Omega}{R_G} \tag{1}$$

Commonly used gains and resistor values are shown in Figure 1.

The  $50k\Omega$  term in equation 1 is the sum of the two feedback resistors of  $A_1$  and  $A_2$ . These on-chip metal film resistors are laser trimmed to accurate absolute values. The accuracy and temperature coefficient of these resistors are included in the gain accuracy and drift specifications of the INA116.

The stability and temperature drift of  $R_{\rm G}$  also affect gain.  $R_{\rm G}$ 's contribution to gain accuracy and drift can be directly inferred from the gain equation (1). Low resistor values required for high gain make wiring resistance important. Sockets add to the wiring resistance that will contribute additional gain error in gains of approximately 100 or greater.

## **OFFSET TRIMMING**

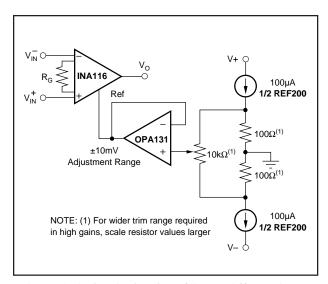

The INA116 is laser trimmed for low offset voltage and offset voltage drift; most applications require no external offset adjustment. Figure 2 shows an optional circuit for trimming the output offset voltage. A voltage applied to the Ref terminal is summed at the output. Op amp A<sub>1</sub> provides a low source impedance for the Ref terminal, assuring good common-mode rejection.

FIGURE 1. Basic Connections.

FIGURE 2. Optional Trimming of Output Offset Voltage.

## INPUT BIAS CURRENT RETURN PATH

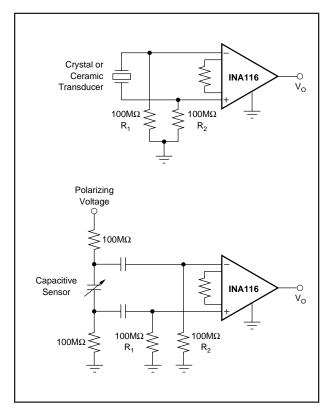

Input circuitry must provide an input bias current path for proper operation. Figure 3 shows resistors  $R_1$  and  $R_2$  to provide an input current path. Without these resistors, the inputs would eventually float to a potential that exceeds the common-mode range of the INA116 and the input amplifiers would saturate. Because of its exceedingly low input bias current, improperly biased inputs may operate normally for a period of time after power is first applied, or operate intermittently.

FIGURE 3. Providing An Input Bias Current Path.

#### CIRCUIT BOARD LAYOUT AND ASSEMBLY

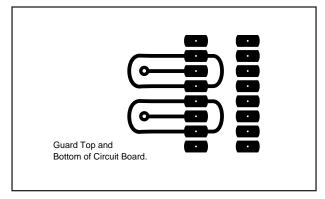

Careful circuit board layout and assembly techniques are required to achieve the exceptionally low input bias current performance of the INA116. Guard terminals adjacent to both inputs make it easy to properly guard the critical input terminal layout. Since traces are not required to run between device pins, this layout is easily accomplished, even with the surface mount package. The guards should completely encircle their respective input connections—see Figure 4. Both sides of the circuit board should be guarded, even if only one side has an input terminal conductor. Route any timevarying signals away from the input terminals. Solder mask should not cover the input and guard traces since this can increase leakage.

FIGURE 4. Circuit Board Guard Layout.

After assembly, the circuit board should be cleaned. Commercial solvents should be chosen according to the soldering method and flux used. Solvents should be cleaned and replaced often. Solvent cleaning should be followed by a deionized water rinse and 85°C bake out.

Sockets can be used, but select and evaluate them carefully for best results. Use caution when installing the INA116 in a socket. Careless handling can contaminate the plastic near the input pins, dramatically increasing leakage current.

A proven low leakage current assembly method is to bend the input pins outward so they do not contact the circuit board. Input connections are made in air and soldered directly to the input pin. This technique is often not practical or production-worthy. It is, however, a useful technique for evaluation and testing and provides a benchmark with which to compare other wiring techniques. The circuit board guarding techniques discussed normally reduce leakage to acceptable levels.

A solid mechanical assembly is required for good results. Nearby plastic parts can be especially troublesome since a static charge can develop and the slightest motion or vibration will couple charge to the inputs. Place a Faraday shield around the whole amplifier and input connection assembly to eliminate stray fields.

#### INPUT CONNECTIONS

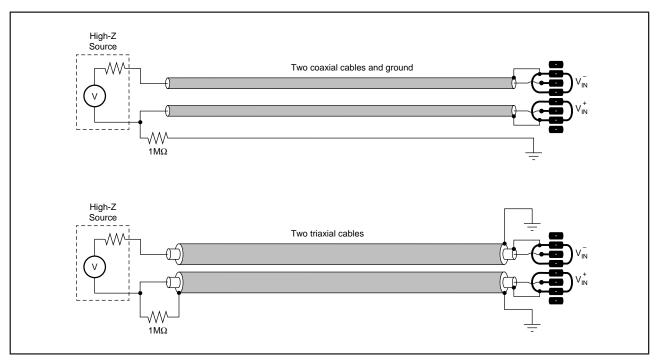

Some applications must make high impedance input connections to external sensors or input connectors. To assure low leakage, the input should be guarded all the way to the signal source—see Figure 5. Coaxial cable can be used with the shield driven by the guard. A separate connection is required to provide a ground reference at the signal source. Triaxial cable may reduce noise pickup and provides the ground reference at the source. Drive the inner shield at guard

potential and ground the outer shield. Two separate guarded lines are required if both the inverting and non-inverting inputs are brought to the source.

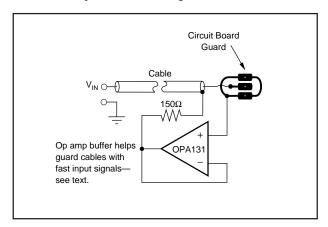

The guard drive output current is limited to approximately  $+2mA/-50\mu A$ . For slow input signals the internal guard output can directly drive a cable shield. With fast input signals, however, the guard may not provide sufficient output current to rapidly charge the cable capacitance. An op amp buffer may be required as shown in Figure 6.

FIGURE 5. Input Cable Guarding Circuits.

FIGURE 6. Buffered Guard Drive.

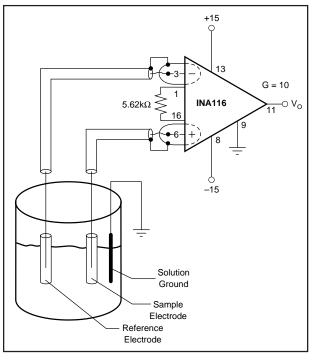

FIGURE 7. pH or Ion Measurement System.