# IRIS4007(K)

### **INTEGRATED SWITCHER**

#### **Features**

- Primary current mode control, and secondary voltage mode control

- Vcc over-voltage protection (latched)

- Over-current and over-temperature protection

- Quasi resonant, variable frequency operation

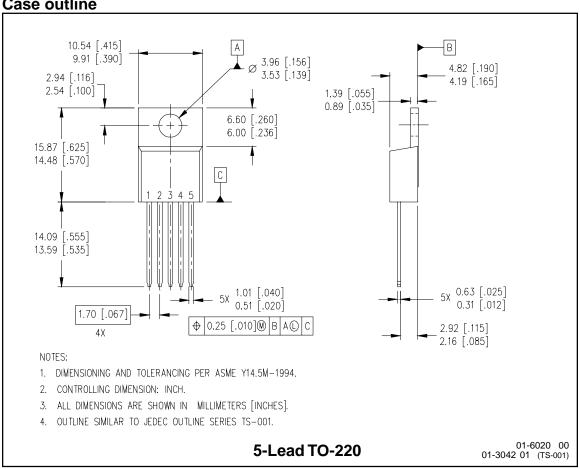

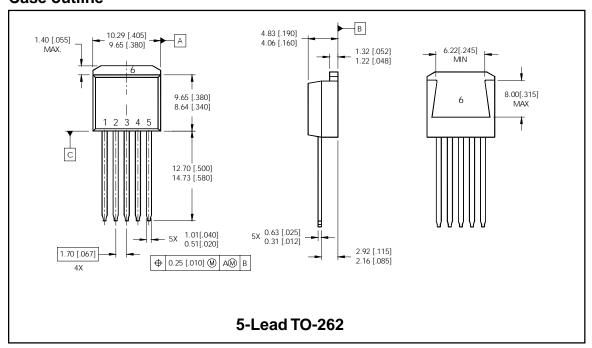

- 5 pin TO-220 and TO-262 package

- 0.4Ω Rds(on) max/ 200V MOSFET

- Fully Characterized Avalanche Energy

#### **Descriptions**

The IRIS4007(K) is a dual mode voltage and current controller combined with a MOSFET in a single Package. The IRIS4007(K) are designed for use in AC/DC and DC/DC switching power supplies upto 100VDC nominal input and is capable of 30W for a nominal 48V input. The device can operate in either a quasi-resonant or Pulse Ratio Control (PRC) mode, and thereby variable frequency operation.

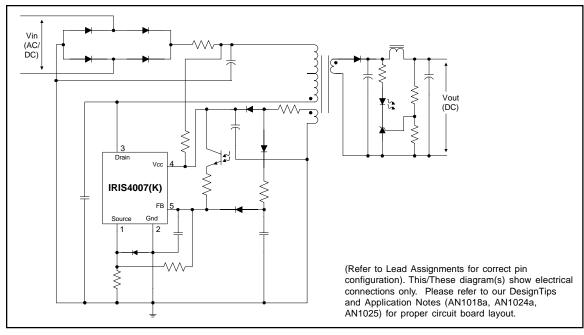

### **Typical Connection Diagram**

### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to terminals stated, all currents are defined positive into any lead. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol              | Definition                               | Terminals | Max. Ratings | Units | Note                                           |

|---------------------|------------------------------------------|-----------|--------------|-------|------------------------------------------------|

| I <sub>D</sub> peak | Peak drain current                       | 3-1       | 20           |       | Single pulse                                   |

| I <sub>D</sub> max  | Maximum switching current                | 3-1       | 4.0          | А     | V <sub>2-3</sub> = 0.78V<br>Tc=25°C            |

| E <sub>AS</sub>     | Single pulse avalanche energy            | 3-1       | 350          | mJ    | V <sub>dd</sub> =50V,L=10mH,<br>Tc=25°C        |

| V <sub>CC</sub>     | Power supply voltage                     | 4-3       | 35           | V     |                                                |

| V <sub>TH</sub>     | OCP/FB terminal voltage                  | 5-2       | 6            | ]     |                                                |

| P <sub>D1</sub>     | Power dissipation for MOSFET             | 3-1 -     | 73           |       | With infinite heatsink                         |

|                     |                                          |           | 1.27         | W     | Without heatsink                               |

| P <sub>D2</sub>     | Power dissipation for control part (MIC) | 4-2       | 0.8          |       | Specified by V <sub>IN</sub> x I <sub>IN</sub> |

| Rth <sub>JC</sub>   | Thermal resistance, junction to case     | _         | 1.7          | °C/W  |                                                |

| TJ                  | Junction temperature                     | _         | -40-125      |       |                                                |

| T <sub>S</sub>      | Storage temperature                      | _         | -40-125      | ]     |                                                |

| Tf                  | Internal frame temperature in operation  | _         | -20-125      | ℃     | Refer to recommended operating temperature     |

| T <sub>OP</sub>     | Ambient operating temperature            | _         | -20-125      | 1     |                                                |

| TL                  | Lead temp. (soldering, 10 seconds)       | _         | 300          |       |                                                |

## **Recommended Operating Conditions**

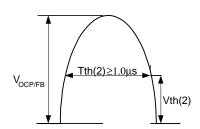

Time for input of quasi resonant signals.

For the Quasi resonant signal inputted to the  $V_{DCP/FB}$  terminal at the time of quasi resonant operation, the signal should be wider thant Tth(2)

### **Electrical Characteristics (for Control IC)**

$V_{CC} = 18V$ ,  $(T_A = 25^{\circ}C)$  unless otherwise specified.

| Symbol                 | Definition                                                   | Min. | Тур. | Max. | Units | Test Conditions                      |

|------------------------|--------------------------------------------------------------|------|------|------|-------|--------------------------------------|

| V <sub>CCUV+</sub>     | V <sub>CC</sub> supply undervoltage positive going threshold | 14.4 | 16   | 17.6 | V     |                                      |

| V <sub>CCUV</sub> -    | V <sub>CC</sub> supply undervoltage negative going threshold | 9    | 10   | 11   | V     |                                      |

| I <sub>QCCUV</sub>     | UVLO mode quiescent current                                  | _    | _    | 100  | μΑ    | V <sub>CC</sub> < V <sub>CCUV+</sub> |

| I <sub>QCC</sub>       | Quiescent operating VCC supply current                       | _    | _    | 30   | mA    |                                      |

| T <sub>OFF/(MAX)</sub> | Maximum OFF time                                             | 40   | _    | 60   |       |                                      |

| T <sub>TH(2)</sub>     | Minimum input pulse width for quasi resonant signals         | _    | _    | 1.0  | μsec  |                                      |

| T <sub>OFF/(MIN)</sub> | Minimum OFF time                                             | _    | _    | 1.5  |       |                                      |

| V <sub>TH(1)</sub>     | OCP/FB terminal threshold voltage 1                          | 0.68 | 0.73 | 0.78 | V     |                                      |

| V <sub>TH(2)</sub>     | OCP/FB terminal threshold voltage 2                          | 1.3  | 1.45 | 1.6  | V     |                                      |

| I <sub>OCP/FB</sub>    | OCP/FB terminal sink current                                 | 1.1  | 1.35 | 1.7  | mA    |                                      |

| V <sub>CC(OVP)</sub>   | V <sub>CC</sub> overvoltage protection limit                 | 20.5 | 22.5 | 24.5 | V     |                                      |

| I <sub>CC(LA)</sub>    | Latch circuit holding current                                | _    | _    | 400  | μΑ    |                                      |

| V <sub>CC(LaOFF)</sub> | Latch circuit reset voltage                                  | 6.6  | _    | 8.4  | V     |                                      |

| T <sub>J(TSD)</sub>    | Thermal shutdown activation temperature                      | 140  | _    | _    | °C    |                                      |

### **Electrical Characteristics (for MOSFET)**

$(T_A = 25^{\circ}C)$  unless otherwise specified.

| Symbol              | Definition                        | Min. | Тур. | Max. | Units | Test Conditions                           |

|---------------------|-----------------------------------|------|------|------|-------|-------------------------------------------|

| V <sub>DSS</sub>    | Drain-to-source breakdown voltage | 200  | _    | _    | V     |                                           |

| I <sub>DSS</sub>    | Drain leakage current             | _    | _    | 250  | μΑ    | Vds=160V, V <sub>CC</sub> =0V             |

|                     |                                   |      |      |      |       | Tj =125°C                                 |

| R <sub>DS(ON)</sub> | On-resistance                     | _    | _    | 0.4  | Ω     | V <sub>3-1</sub> =10V, I <sub>D</sub> =4A |

| t <sub>r</sub>      | Rise time (10% to 90%)            | _    | _    | 200  | ns    |                                           |

| THj-C               | Thermal resistance                | _    | _    | 1.7  | °C/W  | Between junction                          |

|                     |                                   |      |      |      |       | and case                                  |

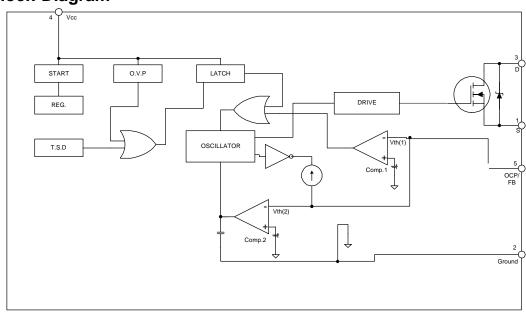

### **Block Diagram**

| Lead Assignments | Pin #                    | Symbol | Description                                                     |

|------------------|--------------------------|--------|-----------------------------------------------------------------|

|                  | 1                        | S      | MOSFET Source terminal                                          |

|                  | 2 Ground Ground terminal |        |                                                                 |

|                  | 3                        | D      | MOSFET Drain terminal                                           |

|                  | 4                        | Vcc    | Control circuit supply voltage                                  |

| 1 2 3 4 5        | 5                        | OCP/FB | Overcurrent detection, and Voltage mode control feedback signal |

#### **Other Functions**

O.V.P. - Overvoltage Protection Circuit

T.S.D. - Thermal Shutdown Circuit

#### **Case outline**

IRIS4007(K)

International

TOR Rectifier

#### **Case outline**

International

**I∷R** Rectifier

IR WORLD HEADQUARTERS: 233 Kansas Street, El Segundo, California 90245 Tel: (310) 252-7105

Data and specifications subject to change without notice. 10/17/2001