# DIVIDE-BY-TWELVE COUNTER | \$5492 [DIVIDE-BY-TWO AND DIVIDE-BY-SIX]

\$5492-A,F,W • N7492-A,F

# DIGITAL 54/74 TTL SERIES

#### DESCRIPTION

The S5492/N7492 is a high-speed monolithic 4-bit binary counter consisting of four master-slave flip-flops which are internally interconnected to provide a divide-by-two counter and a divide-by-six counter. A gated direct reset line is provided which inhibits the count inputs and simultaneously returns the four flip-flops outputs to a logical 0. As the output from flip-flop A is not internally connected to the succeeding flip-flops the counter may be operated in two independent modes:

- 1. When used as a divide-by-twelve counter, output A must be externally connected to input BC. The input count pulses are applied to input A. Simultaneous division of 2, 6, and 12 are performed at the A, C, and D outputs as shown in the truth table.

- 2. When used as a divide-by-six counter, the input count pulses are applied to input BC. Simultaneously, frequency division of 3 and 6 are available at the C and D outputs. Independent use of flip-flop A is available if the reset function coincides with reset of the divide-by-six counter.

The S5492/N7492 is completely compatible with Series 54 and Series 74 logic families. Average power dissipation is 155mW.

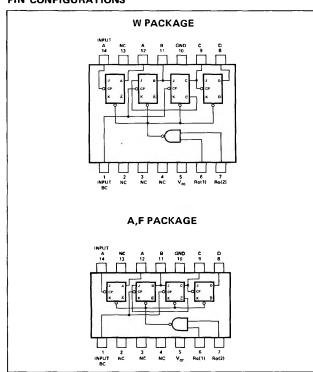

#### PIN CONFIGURATIONS

#### TRUTH TABLE (See Notes 1 and 2)

|       | OUTPUT |   |   |   |  |

|-------|--------|---|---|---|--|

| COUNT | ۵      | С | В | Α |  |

| 0     | 0      | 0 | 0 | 0 |  |

| 1     | 0      | 0 | 0 | 1 |  |

| 2     | 0      | 0 | 1 | 0 |  |

| 3     | 0      | 0 | 1 | 1 |  |

| 4     | 0      | 1 | 0 | 0 |  |

| 5     | 0      | 1 | 0 | 1 |  |

| 0011117 | OUTPUT |   |   |   |  |

|---------|--------|---|---|---|--|

| COUNT   | D      | С | В | Α |  |

| 6       | 1      | 0 | 0 | 0 |  |

| 7       | 1      | 0 | 0 | 1 |  |

| 8       | 1      | 0 | 1 | 0 |  |

| 9       | 1      | 0 | 1 | 1 |  |

| 10      | 1      | 1 | 0 | 0 |  |

| 11      | 1      | 1 | 0 | 1 |  |

- 1. Output A connected to input B.

- 2. To reset all outputs to logical 0, both  $R_{0(1)}$  and  $R_{0(2)}$  inputs must be at logical 1.

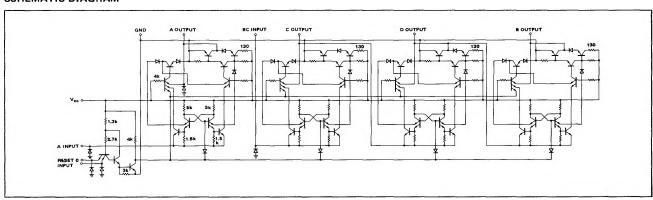

#### SCHEMATIC DIAGRAM

### SIGNETICS DIGITAL 54/74 TTL SERIES - S5492 • N7492

#### RECOMMENDED OPERATING CONDITIONS

| MIN  | NOM                     | MAX                               | UNIT                                                    |

|------|-------------------------|-----------------------------------|---------------------------------------------------------|

| 4.5  | 5                       | 5.5                               | V                                                       |

| 4.75 | 5                       | 5.25                              | v                                                       |

| -55  | 25                      | 125                               | °c                                                      |

| 0    | 25                      | 70                                | °c                                                      |

|      | 1                       | 10                                |                                                         |

| 50   | 1                       |                                   | ns                                                      |

| 50   |                         |                                   | ns                                                      |

|      | 4.5<br>4.75<br>-55<br>0 | 4.5 5<br>4.75 5<br>-55 25<br>0 25 | 4.5 5 5.5<br>4.75 5 5.25<br>-55 25 125<br>0 25 70<br>10 |

#### ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

|                     | PARAMETER                                                        | т:                                               | EST CONDITIONS                                   | *              | MIN        | TYP**    | MAX        | UNIT     |

|---------------------|------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------|------------|----------|------------|----------|

| V <sub>in(1)</sub>  | Input voltage required to ensure logical 1 at any input terminal | V <sub>CC</sub> = MIN                            |                                                  |                | 2          |          |            | V        |

| V <sub>in(0)</sub>  | Input voltage required to ensure logical 0 at any input terminal | V <sub>CC</sub> = MIN                            |                                                  |                |            |          | 0.8        | V        |

| V <sub>out(1)</sub> | Logical 1 output<br>voltage                                      | V <sub>CC</sub> = MIN,                           | $I_{load} = -400\mu A$                           |                | 2.4        |          |            | V        |

| V <sub>out(0)</sub> | Logical 0 output voltage                                         | V <sub>CC</sub> = MIN,                           | I <sub>sink</sub> = 16mA                         |                |            |          | 0.4        | V        |

| lin(1)              | Logical 1 level input current at $R_{O(1)}$ or $R_{O(2)}$ inputs | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |                |            |          | 40<br>1    | μA<br>mA |

| lin(1)              | Logical 1 level input current at input A                         | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |                |            |          | 80<br>1    | μA<br>mA |

| lin(1)              | Logical 1 level input<br>current at input BC                     | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |                |            |          | 160<br>1   | μA<br>mA |

| l <sub>in(0)</sub>  | Logical 0 level input current at $R_{0(1)}$ or $R_{0(2)}$ inputs | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 0.4V                           |                |            |          | -1.6       | mA       |

| lin(0)              | Logical 0 level input<br>current input A                         | V <sub>CC</sub> = MAX,                           | $V_{in} = 0.4V$                                  |                |            |          | -3.2       | mA       |

| l <sub>in</sub> (0) | Logical O'level input<br>current at input BC                     | V <sub>CC</sub> = MAX,                           | $V_{in} = 0.4V$                                  |                |            |          | -6.4       | mA       |

| los                 | Short circuit output current †                                   | V <sub>CC</sub> = MAX,                           | $V_{out} = 0$                                    | S5492<br>N7492 | -20<br>-18 |          | -57<br>-57 | mA<br>mA |

| 'cc                 | Supply current                                                   | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 4.5V                           | S5492<br>N7492 |            | 31<br>31 | 44<br>51   | mA<br>mA |

## SWITCHING CHARACTERISTICS, $V_{CC}$ = 5V, $T_A$ = 25°C, N = 10

|                  | PARAMETER                                                                             | TEST CONDITIONS        |                       | MIN | TYP | MAX | UNIT |

|------------------|---------------------------------------------------------------------------------------|------------------------|-----------------------|-----|-----|-----|------|

| f <sub>max</sub> | Maximum frequency of input count pulses                                               | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω | 10  | 18  |     | MHz  |

| <sup>t</sup> pd1 | Propagation delay time<br>to logical 1 level from<br>input count pulse to<br>output D | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω |     | 60  | 100 | ns   |

| <sup>t</sup> pd0 | Propagation delay time<br>to logical 0 level from<br>input count pulse to<br>output D | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω |     | 60  | 100 | ns   |

<sup>\*</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

\*\* All typical values are at V<sub>CC</sub>= 5V, T<sub>A</sub> = 25°C.

† Not more than one output should be shorted at a time.