Silicon N Channel MOS FET High Speed Power Switching

ADE-208-453 B 3rd. Edition

#### Features

- Low on-resistance

- High speed switching

- Low drive current

- No secondary breakdown

- Avalanche ratings

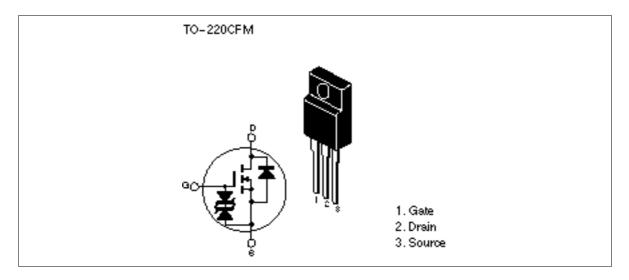

#### Outline

## Absolute Maximum Ratings ( $Ta = 25^{\circ}C$ )

| Item                                      | Symbol                               | Ratings     | Unit |  |

|-------------------------------------------|--------------------------------------|-------------|------|--|

| Drain to source voltage                   | V <sub>DSS</sub>                     | 500         | V    |  |

| Gate to source voltage                    | V <sub>GSS</sub>                     | ±30         | V    |  |

| Drain current                             | ID                                   | 7           | A    |  |

| Drain peak current                        | I <sub>D(pulse)</sub> * <sup>1</sup> | 28          | A    |  |

| Body to drain diode reverse drain current | I <sub>DR</sub>                      | 7           | A    |  |

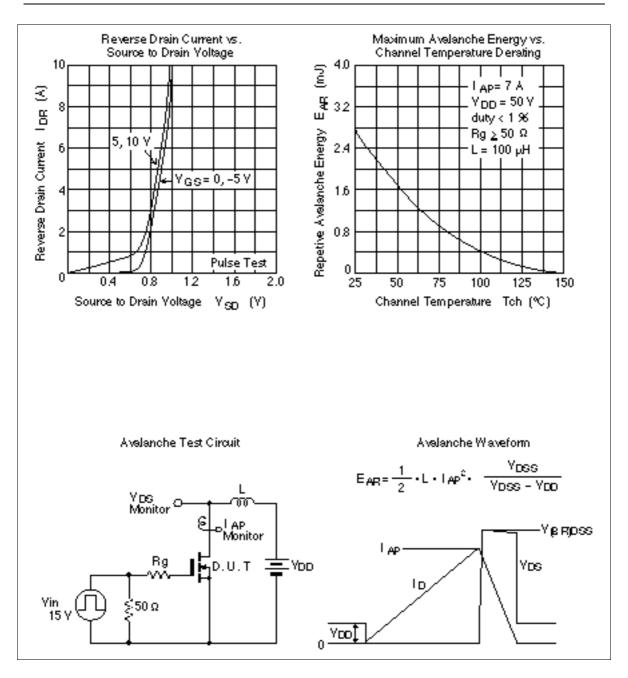

| Avalanche current                         | I <sub>AP</sub> * <sup>3</sup>       | 7           | A    |  |

| Avalanche energy                          | E <sub>AR</sub> * <sup>3</sup>       | 2.7         | mJ   |  |

| Channel dissipation                       | Pch* <sup>2</sup>                    | 30          | W    |  |

| Channel temperature                       | Tch                                  | 150         | °C   |  |

| Storage temperature                       | Tstg                                 | -55 to +150 | °C   |  |

|                                           |                                      |             |      |  |

Notes: 1.  $PW \le 10\mu s$ , duty cycle  $\le 1 \%$

2. Value at Tc = 25°C

3. Value at Tch = 25°C, Rg  $50\Omega$ , L = 100  $\mu$ H

#### **Electrical Characteristics** (Ta = 25°C)

| Item                                       | Symbol               | Min | Тур  | Max  | Unit | Test Conditions                                               |

|--------------------------------------------|----------------------|-----|------|------|------|---------------------------------------------------------------|

| Drain to source breakdown voltage          | $V_{(BR)DSS}$        | 500 | —    | _    | V    | $I_D = 10 mA, V_{GS} = 0$                                     |

| Gate to source breakdown voltage           | $V_{(BR)GSS}$        | ±30 | —    | _    | V    | $I_{G} = \pm 100 \mu A, V_{DS} = 0$                           |

| Gate to source leak current                | I <sub>GSS</sub>     | _   | _    | ±10  | μΑ   | $V_{GS} = \pm 25V, V_{DS} = 0$                                |

| Zero gate voltege drain current            | I <sub>DSS</sub>     | —   | —    | 10   | μA   | $V_{DS} = 500 \text{ V}, \text{ V}_{GS} = 0$                  |

| Gate to source cutoff voltage              | V <sub>GS(off)</sub> | 2.5 | _    | 3.5  | V    | $I_D = 1mA, V_{DS} = 10V^{*1}$                                |

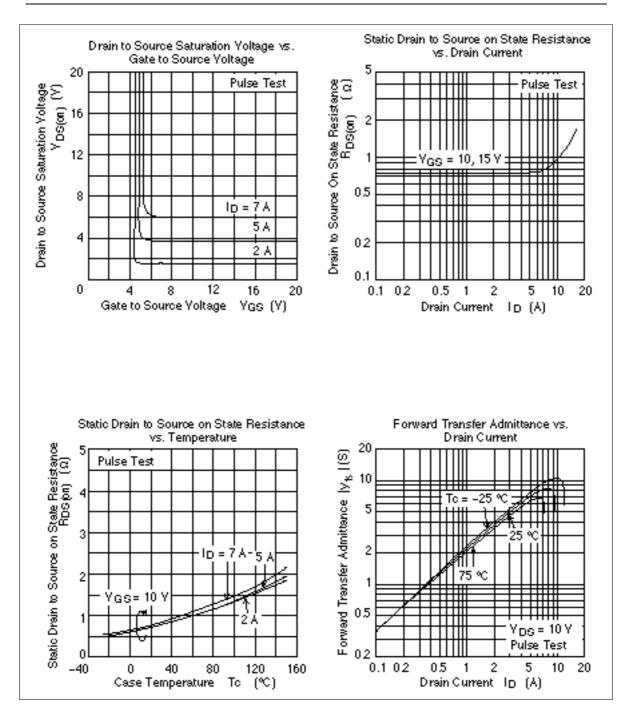

| Static drain to source on state resistance | $R_{\text{DS(on)}}$  | —   | 0.75 | 0.95 | Ω    | $I_D = 4A, V_{GS} = 10V^{*1}$                                 |

| Forward transfer admittance                | y <sub>fs</sub>      | 3.5 | 6.0  | _    | S    | $I_D = 4A, V_{DS} = 10V^{*1}$                                 |

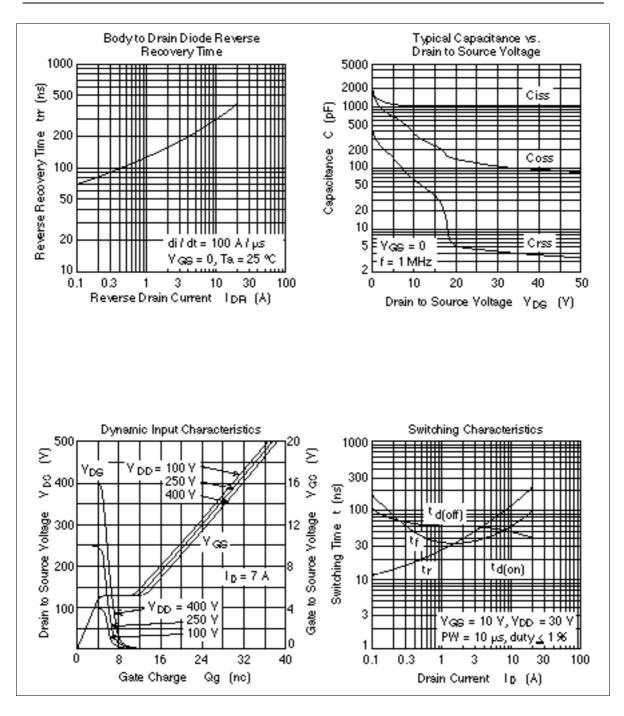

| Input capacitance                          | Ciss                 | _   | 1100 | _    | pF   | V <sub>DS</sub> = 10V                                         |

| Output capacitance                         | Coss                 | _   | 330  | _    | pF   | $V_{GS} = 0$                                                  |

| Reverse transfer capacitance               | Crss                 | _   | 65   | _    | pF   | f = 1MHz                                                      |

| Total gate charge                          | Qg                   | _   | 21   | _    | nc   | $V_{DD} = 400 V$                                              |

| Gate to source charge                      | Qgs                  | _   | 5    | _    | nc   | V <sub>GS</sub> = 10V                                         |

| Gate to drain charge                       | Qgd                  | _   | 8    | _    | nc   | $I_D = 7A$                                                    |

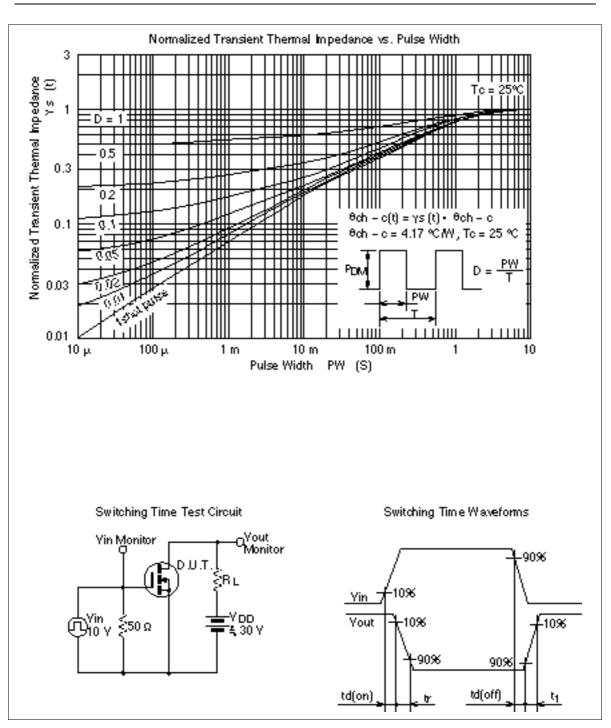

| Turn-on delay time                         | t <sub>d(on)</sub>   | _   | 20   | _    | ns   | $V_{GS}$ = 10V, $I_D$ = 4A                                    |

| Rise time                                  | tr                   | _   | 65   | _    | ns   | $R_L = 7.5\Omega$                                             |

| Turn-off delay time                        | t <sub>d(off)</sub>  | _   | 60   |      | ns   |                                                               |

| Fall time                                  | t <sub>f</sub>       | _   | 40   | —    | ns   |                                                               |

| Body to drain diode forward voltage        | $V_{\text{DF}}$      | _   | 0.95 |      | V    | $I_D = 7A, V_{GS} = 0$                                        |

| Body to drain diode reverse recovery time  | t <sub>rr</sub>      |     | 260  | _    | ns   | I <sub>F</sub> = 7A, V <sub>GS</sub> = 0<br>diF/ dt = 100A/µs |

Note: 1. Pulse test

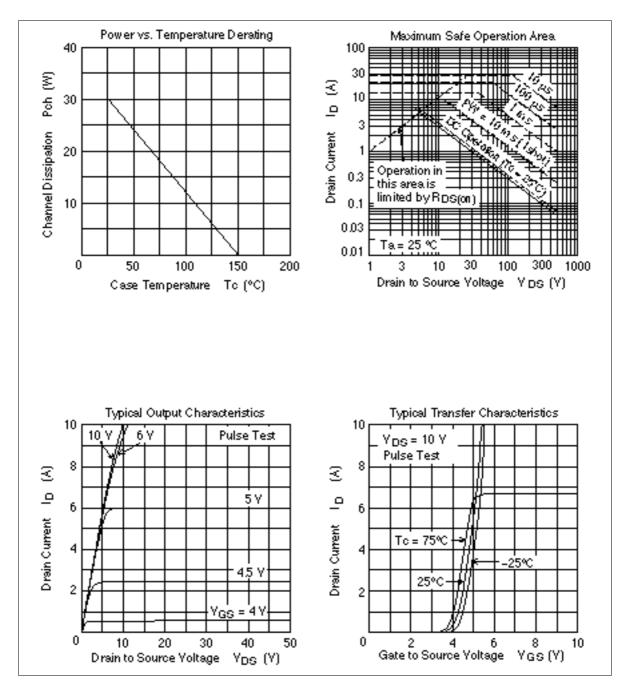

#### **Main Characteristics**

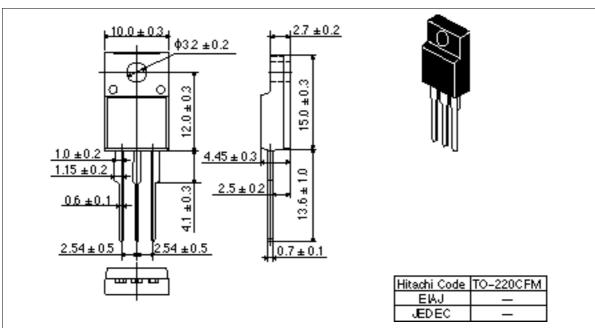

## Package Dimensions

Unit: mm

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

# HITACHI

Hitachi, Ltd. Semiconductor & IC DW. Nippon Bidg., 2-5-2, Chie-machi, Chiyoda-ku, Tokyo 100, Japan Tet Tokyo (03, 3270-2111) Fex: (03, 3270-5109)

For Turther in forms for write to : Hitschi America, Ud Semiconductor & IC Div. 2000 Sierre Point Perfavey Brabene, CA. 94005-4835 USA Tet 445-583-8300 Fex: 445-583-4207

Hitschi Burope GmbH Bedronic Components Group Continentel Burope Domscher Streiße 3 D-85522 Feldkinchen Manchen Tet 059-9 91 80.0 Fex 059-9 29 30 00 Hitschi Burope Ltd. Bectronic Components Div. Northern Burope Hesdquerters Whitebrock Fank Lower Cockhem Road Naiderhesd Berkshire SL63YÅ United Kingdom Tet 0625-535000 Fat: 0625-778322 Hitschi Asia Pte. Ltd +5 Collyer Gusy #20-00 Hitschi Tower Snappore 0104 Tet 535-2100 Fax: 535-1533

Hitschi Asia (Hong Kong) Ltd. Unit 706, North Towar, World Finance Cantra, Harbour City, Carton Road Taim Sha Tau, Kowloon Hong Kong Tet 27359218 Fax: 27359218

Copyright @Hitschi, Ltd., 1997. All rights reserved. Printed in Jepen.